Series: Electronics and Energetics Vol. 33, No 2, June 2020, pp. 155-167

https://doi.org/10.2298/FUEE2002155R

## FLASH MEMORY DEVICES WITH METAL FLOATING GATE/METAL NANOCRYSTALS AS THE CHARGE STORAGE LAYER: A STATUS REVIEW

### Renu Rajput, Rakesh Vaid

Department of Electronics, University of Jammu, Jammu, India

**Abstract**. Traditional flash memory devices consist of Polysilicon Control Gate (CG) – Oxide-Nitride-Oxide (ONO - Interpoly Dielectric) - Polysilicon Floating Gate (FG) -Silicon Oxide (Tunnel dielectric) - Substrate. The dielectrics have to be scaled down considerably in order to meet the escalating demand for lower write/erase voltages and higher density of cells. But as the floating gate dimensions are scaled down the charge stored in the floating gate leak out more easily via thin tunneling oxide below the floating gate which causes serious reliability issues and the whole amount of stored charge carrying information can be lost. The possible route to eliminate this problem is to use high-k based interpoly dielectric and to replace the polysilicon floating gate with a metal floating gate. At larger physical thickness, these materials have similar capacitance value hence avoiding tunneling effect. Discrete nanocrystal memory has also been proposed to solve this problem. Due to its high operation speed, excellent scalability and higher reliability it has been shown as a promising candidate for future non-volatile memory applications. This review paper focuses on the recent efforts and research activities related to the fabrication and characterization of non-volatile memory device with metal floating gate/metal nanocrystals as the charge storage layer.

**Key words**: Metal oxide semiconductor (MOS), non-volatile memory (NVM), nanocrystal (NC), dielectrics, interpoly dielectric (IPD), floating gate (FG)

### 1. Introduction

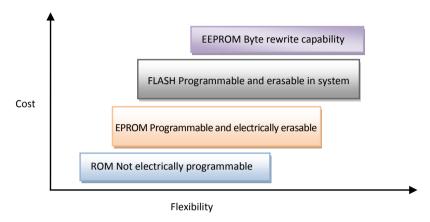

Flash memory is the extensively used non-volatile information-storage device today because of its multi-bit per cell storage property and lesser cost per bit. Moreover its fabrication process is consistent with the present CMOS process and is a relevant solution for embedded memory applications. The qualitative comparison of various non-volatile MOS memory devices in the flexibility-cost plane [1] is shown in Fig.1. NOR flash memory and NAND flash memory are the two main types of flash memory used today. The key difference between the two is that NOR flash memory allow a single byte

Received December 26, 2019

Corresponding author: Rakesh K. Vaid

Department of Electronics, University of Jammu, Jammu-180006, India

(E-mail: rakeshvaid@ieee.org)

to be written to an erased location or read independently where as NAND flash memory is written in blocks or pages. The other contrast is that the former uses channel hot electron (CHE) for programming and has slower program-erase speed while the later uses fowler-nordheim tunneling for programming and has fast program-erase speed.

Fig. 1 Non-volatile MOS memory qualitative comparison in the flexibility-cost plane [1]

NAND flash memory finds use in data storage devices like mobile phones, pen drives, digital cameras etc. and the NAND flash based solid state drive (SSD) is used as a replacement for hard disk drive (HDD) in modern computers and laptops. The growing demand for this technology is the key driving force to increase the data storage capacity and decrease the cost per bit in flash memories by scaling down the flash cell to smaller and smaller dimensions. In continual scaling the major roadblocks are being faced by both NOR and NAND flash memories. The scaling projection for floating-gate NOR and NAND flash memory by International Technology Roadmap for Semiconductors (ITRS) [2] is shown widely in Table 1 and 2. MOS memory devices rely on the charge stored in the floating gate to cause a shift in the threshold/flatband voltage. The schematic cross section of a floating-gate MOS memory cell is shown in Fig.2.

Fig. 2 Schematic cross section of MOS memory cell

Conventionally, the floating gate and control gate are usually made of Polysilicon. The tunneling barrier and the blocking oxide are typically composed of SiO<sub>2</sub> and oxidenitride-oxide (ONO) respectively. Floating gate acts as a potential well and once the charges are injected into the potential well, it cannot move without external electric field. The programming and erasing of the memory cell is carried out by applying positive and negative electric field to the control gate respectively. Si has been used in MOS technology for many decades because of the better qualities of its native oxide [3]. In advanced semiconductor technology, the transistor gate length will continue to shrink in order to achieve faster switching speed and high device density. This results in reduction of gate length and gate oxide thickness to 1.5nm and oxide scaling down to EOT of approx. 0.5nm is required [4]. As the thickness of SiO<sub>2</sub> shrinks below 1.5nm, it is facing its physical limitations because of gate dielectric leakage current and reliability requirements [5]. Thus there is a need for alternate channel materials that can enhance channel mobility beyond the physical limits of Si based MOS devices [6]. With the decrease in thickness of tunnel dielectric, the interface between Si and SiO<sub>2</sub> plays a very important role in retaining the charge for the long time. However, for a very thin SiO2, it is impossible to have a defect free oxide and even a single defect can cause leakage of charge stored in floating gate through the tunnel oxide. Thus, thinner tunnel dielectric would degrade the charge retention. For instance, with 2.3 nm SiO<sub>2</sub> tunneling oxide shows reasonable programming efficiency with fairly low programming voltage, but loose 25% of its stored charges in several tens of seconds [7]. To overcome these issues, SiON (Silicon oxynitride) and other high dielectric constant materials with higher physical thickness are being used to limit the leakage current while maintaining the higher capacitance values of the scaled devices. SiON has been used as a substitute for SiO<sub>2</sub> because of its high dielectric permittivity and low density of surface states. In addition, by differing O/N ratio the band energy of SiON can be tailored between 5 and 9 eV [8, 9]. The tunnel oxide has the most strict requirements in a flash cell with properties summarized as under: a) It must provide a good interface to the silicon channel for reliable transistor operation b) It should provide efficient charge transport either through tunneling or hot carrier injection during the programming and erase operations which allow the data to be changed in the memory cell c) It should enable years of charge retention on the floating gate [10]. The conventional polysilicon floating gate structure suffers from various disadvantages like cell to cell interference when optimized for high density, high leakage current through tunneling dielectric, programming current become increasingly ballistic and loss of gate coupling factor. The thickness of ONO is to be reduced to compensate for the loss of gate coupling factor. But when it is reduced below 10nm, it would cause increase in the unwanted gate to gate tunneling and degrade the retention characteristics of memory devices. The possible route to eliminate this problem is to use high-k based interpoly dielectric and to replace the polysilicon floating gate with a metal floating gate. The added benefits of incorporating a metal floating gate include work function tunability, higher density of states and most importantly the lower ballistic transport. The lower ballistic transport in case of metals is a beneficial factor in scaling down the floating gate thickness to realize a lower cell-to-cell interference [11]. Hf based high-k dielectrics in combination with metal floating gate demonstrated excellent memory characteristics [12]. Therefore, the ultra-thin metal floating gate is a promising candidate for future scaled NOR and NAND FLASH memories.

**Table 1** Scaling projections for floating-gate NOR flash by International Technology Roadmap for Semiconductors (ITRS) [2]

| NOR   | NOR Flash  | Gate length | Tunnel oxide | Interpoly  | Interpoly     | Gate      | Retention |

|-------|------------|-------------|--------------|------------|---------------|-----------|-----------|

| Flash | Technology | Physical    | thickness    | Dielectric | dielectric    | Coupling  | (years)   |

|       | node-F     | (nm)        | (nm)         | material   | thickness EOT | Ratio     |           |

|       | (nm)       |             |              |            | (nm)          |           |           |

| 2011  | 40         | 100         | 8-9          | ONO        | 13-15         | 0.6-0.7   | 10-20     |

| 2012  | 35         | 100         | 8-9          | ONO        | 13-15         | 0.6 - 0.7 | 10-20     |

| 2013  | 32         | 90          | 8            | High-k     | 8-10          | 0.6-0.7   | 20        |

| 2014  | 28         | 90          | 8            | High-k     | 8-10          | 0.6 - 0.7 | 20        |

| 2015  | 25         | 90          | 8            | High-k     | 8-10          | 0.6-0.7   | 20        |

| 2016  | 22         | (?)         | (?)          | High-k     | 8-10          | 0.6 - 0.7 | 20        |

| 2017  | 20         | (?)         | (?)          | High-k     | 8-10          | 0.6-0.7   | 20        |

| 2018  | 28         | (?)         | (?)          | High-k     | 7-9           | 0.6 - 0.7 | 20        |

| 2019  | 16         | (?)         | (?)          | High-k     | 6-8           | 0.6-0.7   | 20        |

| 2020  | 14         | (?)         | (?)          | High-k     | 6-8           | 0.6 - 0.7 | 20        |

| 2021  | 12         | (?)         | (?)          | High-k     | 6-8           | 0.6-0.7   | 20        |

| 2022  | 10         | (?)         | (?)          | High-k     | 6-8           | 0.6 - 0.7 | 20        |

| 2023  | 10         | (?)         | (?)          | High-k     | 6-8           | 0.6-0.7   | 20        |

| 2024  | 10         | (?)         | (?)          | High-k     | 6-8           | 0.6 - 0.7 | 20        |

**Table 2** Scaling projections for floating-gate NAND flash by International Technology Roadmap for Semiconductors (ITRS) [2]

| NAND<br>Flash | NAND Flash<br>Technology | Tunnel oxide | Interpoly<br>Dielectric | Interpoly dielectric | Control gate | Gate<br>Coupling | Retention (years) |

|---------------|--------------------------|--------------|-------------------------|----------------------|--------------|------------------|-------------------|

|               | node-F                   | thickness    | material                | thickness            | material     | Ratio            |                   |

|               | (nm)                     | (nm)         |                         | EOT                  |              |                  |                   |

|               |                          |              |                         | (nm)                 |              |                  |                   |

| 2011          | 28                       | 6-7          | ONO                     | 10-13                | n-poly       | 0.6-0.7          | 10-20             |

| 2012          | 25                       | 6-7          | High-k                  | 9-10                 | Poly/metal   | 0.6 - 0.7        | 10-20             |

| 2013          | 22                       | 6-7          | High-k                  | 9-10                 | Poly/metal   | 0.6-0.7          | 10-20             |

| 2014          | 20                       | 6-7          | High-k                  | 9-10                 | Poly/metal   | 0.6 - 0.7        | 10                |

| 2015          | 19                       | 6-7          | High-k                  | 9-10                 | metal        | 0.6-0.7          | 5-10              |

| 2016          | 18                       | 4            | High-k                  | 9-10                 | metal        | 0.6 - 0.7        | 5-10              |

| 2017          | 16                       | 4            | High-k                  | 9-10                 | metal        | 0.6-0.7          | 5-10              |

| 2018          | 14                       | 4            | High-k                  | 9-10                 | metal        | 0.6 - 0.7        | 5-10              |

| 2019          | 13                       | 4            | High-k                  | 8-10                 | metal        | 0.6-0.7          | 5-10              |

| 2020          | 12                       | 4            | High-k                  | 8-10                 | metal        | 0.6 - 0.7        | 5-10              |

| 2021          | 11                       | 4            | High-k                  | 8-10                 | metal        | 0.6-0.7          | 5-10              |

| 2022          | 9                        | 4            | High-k                  | 8-10                 | metal        | 0.6-0.7          | 5-10              |

| 2023          | 8                        | 4            | High-k                  | 8-10                 | metal        | 0.6-0.7          | 5-10              |

| 2024          | 8                        | 4            | High-k                  | 8-10                 | metal        | 0.6-0.7          | 5-10              |

Initially in 1967, Charge-trapping memory (CTM) was introduced to illustrate some eminent advantages over the conventional floating-gate counterpart [13]. Recently, floating gate memory devices consisting of discrete metal nanocrystals have received huge attention due to their excellent memory performance and high scalability. Memory devices with nanocrystal floating-gate offer faster write/erase speeds, lower power

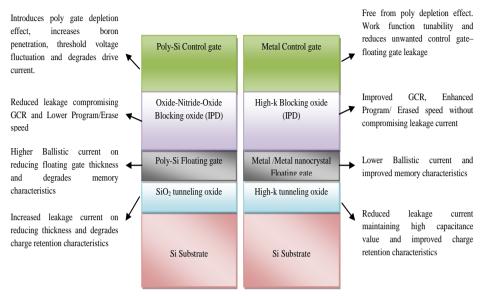

consumption, and more powerful endurance characteristics compared to conventional continuous floating-gate nonvolatile memory devices. During the last few years, Si and Ge nanocrystals embedded in gate oxide layers have been studied as the charge storage nodes in Silicon-based memory devices. But it has been found that during the device fabrication their retention characteristics are very sensitive to the thermal process because of the existence of defects and traps inside or at the surface of the nanocrystals. The presence of these defects and traps limits the application of Si and Ge nanocrystals in nonvolatile memory. Thus the use of metal nanoparticles has been proposed to prolong the retention characteristics and to overcome the limits of semiconductor nanocrystals [14]. The fabrication of a discrete non volatile memory (NVM) cell requires a perfect control of four main parameters: (a) the tunnel oxide thickness (b) the nanocrystal density (c) the nanocrystal diameter and (d) the control oxide thickness. The most commonly used methods to fabricate nanocrystals are self-assembly, precipitation and chemical reaction. In self assembly procedure, a trapping layer of 1-5 nm is deposited and then the film is annealed at a temperature close to its eutectic temperature in an inert gas ambient to transform the trapping layer into a nanocrystal structure. The diameter of the nanocrystal depends on the thickness of the trapping layer as well as the temperature and duration of the thermal treatment. However this method cannot make sure that the trapping layer is completely discrete. In precipitation method, an oversaturated or mixed trapping layer is prepared by ion implantation into a deposited insulator layer or codeposit system to form nanocrystals by further thermal annealing. However, this method has also some limitations due to use of high energy ion implantation for formation of nanocrystals. The chemical reaction method is most widely used to form a nanocrystal trapping layer. Initially, a binary or tertiary mixed layer is co-deposited by different material systems and then the layer is oxidized by RTA under an oxygen flow. But the control of the oxygen concentration in the mixed layer is an important issue. A low oxygen concentration causes insufficient oxidation of the mixed layer and higher leakage current and a high oxygen concentration can result in the oxidation of the nanocrystal. The memory property can be lost if either of these two conditions occur. A metallic nanocrystal storage layer has several advantages over the semiconductor nanocrystal storage layer due to their high density of states and work function engineering. The large work function difference between the metal and the Si substrate creates a deep potential well that ensures a lesser charge loss ultimately resulting in enhancement of the retention characteristics. Blocking layers comprised of high-k dielectrics allow the use of relatively thick films which prevent leakages while maintaining a thin equivalent oxide thickness (EOT) and prevent any charge leakage to the top gate. Moreover, the increased capacitance density offered by high-k films enlarges the charge storage density. Fig. 3 shows the schematic diagram enlightening the motivation and challenges in transitioning from conventional memory structure to a novel high-k MOS memory structure.

Fig. 3 Schematic diagram showing the comparison between conventional and novel high-k MOS memory structure

# 2. RELATED WORK TO NON-VOLATILE MEMORY STRUCTURES USING DIFFERENT METAL NANOCRYSTALS/METAL FLOATING GATE

Self-assembly of metal nanocrystals including Au, Ag, and Pt on ultrathin oxide for nonvolatile memory applications were investigated [15] and it was observed that for non volatile memory cells spherical nanocrystals are preferred because the three dimensional symmetry results in the best charge confinement and physical stability from surface energy minimization. The shallow potential well in case of semiconductor nanocrystals (Si nanocrystals paired with a Si substrate) can only hold charges for a relatively short time because of direct-tunneling back to the substrate [16]. However, metal nanocrystals due to their large work functions can make use of the deep potential wells to hold electrons for longer time and thus the memory effects of Au and Pt are better than the Ag. Chungho Lee et. al. [17] in 2005 fabricated and characterized the heterogeneousstack devices consisting of metal nanocrystals (Au) and silicon nitride (Si<sub>3</sub>N<sub>4</sub>). The metal nanocrystals at the lower stack allow the direct tunneling mechanism during program/erase to achieve low-voltage operation and good endurance while the nitride layer at the upper stack acts as an additional charge trap layer to increase the memory window and significantly improve the retention time. Semiconductor nanocrystal (Si) and nitride heterogeneous stacks have been first proposed in metal-nitride-oxide-silicon (MNOS) structure by Yamazaki et al. [18, 19] and SONOS structure by Steimle et al. [20, 21]. The nanocrystal/nitride heterogeneous stack shows enlarged charge storage capacity, longer retention, low voltage and fast P/E by additional nitride traps as compared to Au nanocrystals. Ch Sargentis et. al [22] in 2005 fabricated a novel MOS memory device with platinum (Pt) nanoparticles embedded in the HfO2 /SiO2 interface which exhibits clear hysteresis behavior and is attributed to the charge storage in the nanoparticles. Jong Jin Lee and Dim-Lee Kwong [23] in 2005 proposed a nonvolatile memory using nickel nanocrystal (NC) embedded in HfO<sub>2</sub> tunneling/control dielectrics to overcome the fundamental tradeoff between programming and data retention characteristics. Nickel has not only suitable work function (4.5-4.6 eV) [24] for such applications but it also exhibits a low anneal temperature for NC formation which is advantageous to the quality of underlying tunneling HfO<sub>2</sub> dielectrics (5.1nm). Hei Wong and Hiroshi Iwai in 2006 [25] suggested that the conventional oxide can be scaled down to two atomic layers of about 7A ° but this is not viable in practice because of the non-scalabilities of interface, trap capture cross-section, leakage current and the statistical parameters of fabrication processes. Physically thicker high-k material can help to solve most of the problems but high-k gate dielectric film still give rise to several reliability problems and degrades the performances of the MOS devices to a great extent. Bulk oxynitride/high-k stack could be a secure solution to this problem. The major benefits of oxynitride are that most of its material characteristics are second to SiO<sub>2</sub> but with a larger value of dielectric constant (3.9-7.8), band gap within 5.9-8.9 eV, conduction band offset greater than 2.1 eV, thermally stable structure with high crystallization temperature and stable on silicon. It also has a comparatively better dielectric/Si interface when compared to other high-k competitors. These properties are sufficient for MOS device applications. But the two atomic-layer oxynitride will not be synthesized and the leakage current will be too large as well. Therefore, a better solution is to make use of the bulk oxynitride/high-k stack to make it physically thicker and thus reduce the gate tunneling current and the sensitivity to thickness fluctuation. Due to the fabrication methods, most of the defects in oxynitride are tied to the hydrogen and hydroxyl groups and are the major sources for hot-carrier induced related trap generation in nitrided oxide films [26-29]. Hence it is very important to minimize the hydrogen incorporation for a highly reliable oxynitride film for advanced MOS device applications. S. Hwang et. al [30] in 2007 studied the effect of the presence of high concentration of nitrogen in silicon-oxide layer. The results reveal the suitability of oxynitride films in high quality ultra-thin-film transistors and non volatile memory device. P.H. Yeh et. al. [31] in 2007 review the memory effects of the Ni, NiSi<sub>2</sub>, CoSi<sub>2</sub> and NiSi<sub>2</sub> with SiO<sub>2</sub>/HfO<sub>2</sub> tunneling dielectrics. It was found that the memory effects of the metal nanocrystals have strong relationship with the work function and the work function can be modulated by changing the metal species. The memory window of the samples with HfO<sub>2</sub> as tunnel dielectric is larger than the samples with SiO<sub>2</sub> due to the smaller voltage drop with the same physical thickness(=3nm). The physical thickness of HfO<sub>2</sub> tunnel oxide is sufficient for the small operation voltage but not satisfactory for the retention requirement because the equivalent oxide thickness (1.5 nm) being too thin so that the electrons can tunnel back easily. The tunneling probability of electron is interrelated with the thickness and the barrier of the tunnel dielectric. Weihua Guan et. al. [32] in 2007 proposed that metal nanocrystal (MNC) shows better retention performance than SNC (semiconductor nanocrystals) for the same nanocrystal size because of the higher electron barrier height from MNC to the substrate and the weaker quantum confinement effect of MNC. A tunneling oxide of 3.6 nm is thick enough to guarantee 10 years retention for Au nanocrystal. It is also observed that high-k tunneling barrier combined with high work function MNC (e.g.NC- Au) can further enhance the retention performance. Therefore, metal nanocrystal memory devices employing high-k gate dielectric is a promising

candidate for the application of non-volatile memories. Again, Weihua Guan et. al. [33] in 2007 fabricated MOS capacitor structure with metal nanocrystals (including Au, Ni and Co formed by self-assembling process) embedded in the gate oxide for nonvolatile memory (NVM) application. Due to high work function (5.0 eV) Au nanocrystals can provide enhanced retention performance which confirms the high capacity of Au nanocrystals for NVM applications with respect to semiconductor counterparts. Jae-Young Choi et. al. [34] in 2007 fabricated nonvolatile memory (NVM) MOS capacitors with a structure of Si/SiO<sub>2</sub>/Ni NCs/SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>. The MOS memory structures with the Ni-NC floating gates showed a relatively large memory window of 3-5 V for 10 ms - 1 sunder ±19 V and excellent endurance characteristics. Byoungjun Park et. al. [14] in 2008 studied the electrical characteristics of titanium (Ti) nanoparticles embedded metal-oxidesemiconductor (MOS) capacitors and metal-oxide-semiconductor field effect transistors (MOSFETs) with blocking Al<sub>2</sub>O<sub>3</sub> layer(~20 nm) and tunneling SiO<sub>2</sub> (~6.3 nm)layer. Due to work function of 4.3 eV Ti nanoparticles shows potential for charge storage nodes in floating gate devices because during their formation their surfaces are natively covered with a titanium dioxide (TiO<sub>2</sub>) laver which are known as a high-k dielectric material ( $\varepsilon =$ 80~110) and it can avert the lateral transportation of charge carriers between the Ti nanoparticles and blocking oxide layers and the charge loss through the tunneling barrier. Yingtao Li and Su Liu [35] in 2009 used the different work function NC materials (Au~5.0ev, W~4.6ev and Si~4.05ev) in NVM devices and observed that Au-NC as floating gates exhibit better retention characteristics due to its larger work function which induces a higher barrier height and a deeper well at the interface of the floating gate and the tunneling dielectric. The work function values for some important transition metals are listed in Table 3. Ni Henan et. al. [36] in 2009 fabricated and characterized the MOS structure with double-layer heterogeneous nanocrystals (Si nanocrystals and Ni nanocrystals) embedded in a gate oxide (SiO<sub>2</sub>) matrix for nonvolatile memory applications. The additional metal nanocrystals layer allows the direct tunneling mechanism to raise the flat voltage shift and prolong the retention time. Coulomb blockade and energy level quantization limits the leakage mechanism that is tunneling to the closest lower nanocrystals [37]. Zs. J. Horvath and P. Basa [38] in 2009 created MNOS structures with semiconductor nanocrystals at the Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> interface and summarized that the formation of nanocrystals in nitride based memory structures can enhance both the charging and retention behaviour due to direct tunneling to nanocrystals and creating deep energy states respectively [39,40]. Jeng Hwa Liao et. al. [41] investigated the relationship between the physical and the electrical characteristics of silicon oxynitride (SiON) films and the refractive index. It was found that the charge-trap density of the SiON film is inversely proportional to the oxygen concentration in the SiON layers and the dielectric constant is directly proportional to the refractive index. S. Raghunathan et. al. [11] in 2009 investigated that during programming ultra-thin metal FG shown three orders of magnitude lesser ballistic current than poly-Si of same thickness because the metal has high density of states and larger the density of states the larger is the scattering. It was also observed that the deeper work-function metal FG device erases slower but shows better retention compared to a shallower work-function FG device. Srikant Jayanti et. al. [12] in 2010 investigated ultrathin TaN metal floating gate with Hf based high-k IPD for NAND Flash applications. The results indicate that high-k based interpoly dielectric in combination with ultra-thin TaN metal FG can enable further scaling of NAND Flash memory beyond conventional oxide-nitride-oxide (ONO) based IPD technology. Jang-Sik Lee [42] in 2010 reviewed gold nanoparticles are chemically stable and have a high work function, they have been shown to be a promising candidate for use as the charge trapping element in non-volatile memory devices employing nanoparticles. Shiqian Yang et. al. [43] in 2010 fabricated MOS capacitor (p-Si/SiO<sub>2</sub>/TiW NCs/Al<sub>2</sub>O<sub>3</sub>/Al) and illustrate that high-k blocking oxide play vital role in the low-voltage operation and increases the coupling ratio to the NC layer which results in good charge storage feature. V. Mikhelashvili et. al. [44] in 2010 proposed and demonstrated a double-layer memory capacitor comprising of two Au nanoparticle layers separated by HfO<sub>2</sub> film. HfO<sub>2</sub> was also used for the tunneling layer whereas the blocking insulator was based on a HfN/HfTiO multilayer stack having a dielectric constant larger than 35. The structure exhibits excellent performance in terms of the hysteresis window, the stored charge density, the leakage current, the EOT and its retention properties. G. Gay et. al. [45] in 2010 fabricated the devices with TiN NCs embedded in SiN and observed that the devices were erased 10<sup>2</sup> faster and shows large memory window (10 V) as compared to devices with pure SiN trapping layer. Larysa Khomenkova et. al. [46] in 2011 demonstrated the application of pure HfO<sub>2</sub> and HfSiO layers fabricated by RF magnetron sputtering as alternative tunnel layers for high-k/Si-NCs-SiO<sub>2</sub>/SiO<sub>2</sub> memory structures and indicates the utility of these stack structures for lowoperating-voltage NVM devices with specific deposition conditions and annealing treatment. G. X. Li [47] et. al. in 2011 demonstrated that Hf-rich films tend to form thicker interfacial layer due to the stability of HfO<sub>2</sub> whereas Ti-rich films usually demonstrate higher leakage current owing to the low band gap of TiO2. Overall, the 20-nm-thick films with Hf/Ti ratio of 46/54 exhibit high permittivity up to 50 while maintaining the relatively low leakage current of  $1.2 \times 10^{-8}$  A/cm<sup>2</sup> at 1 V bias which would be the promising candidate to replace HfO<sub>2</sub> for the next generation technology. Minseong Yun [48] et. al. in 2012 demonstrated high density multi-layer Pt nanoparticle embedded memory device with enhanced memory window and better retention property. Chih-Ting Lin et. al. [49] in 2013 revealed that the memory window becomes larger at elevated annealing temperatures due to the high density of Au-NCs. The optimized annealing condition was 700°C because of the large space between NCs. Jun-Hyuk Seo et. al. [50] in 2013 fabricated a MOS capacitor containing Au nanocrystals in a stepped HfO<sub>2</sub> and SiO<sub>2</sub> tunneling oxide matrix. Memory window effects were observed due to the successive charge trapping in Au nanocrystals by controlling the electric field distribution via the tunneling oxide. Wen-Chieh Shih et. al. [51] in 2013 studied MYTOS device i.e metal-yttrium oxide-tantalum oxide-silicon oxide-silicon (Al/Y<sub>2</sub>O<sub>3</sub>/Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub>/Si) and showed that the large conduction band offset at the Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> and the Y<sub>2</sub>O<sub>3</sub>/Ta<sub>2</sub>O<sub>5</sub> interfaces is expected to give better blocking efficiency which will improve memory window and programming speed and can also relieve over erase problem. Guoxing Chen et. al. [52] in 2014 demonstrated that metal floating gate capacitor Si/SiO<sub>2</sub>-2.7/HfO<sub>2</sub>-8/TaN-8/Al<sub>2</sub>O<sub>3</sub>-15/Au-150 presents favorable performance with lower operation voltage as well as enhanced program/erase speed and improvement of data retention compared to Si/SiO<sub>2</sub>-4.5/TaN-8/Al<sub>2</sub>O<sub>3</sub>-15/Au-150 floating gate cell. Thus, the program/erase speed can be enhanced using a high-k blocking layer. Metal oxides shows potential for the high-k gate materials because of chemical stability at Si interface. Table 4 shows the contrast of a few main properties of high-k dielectric materials [53]. High-k dielectrics proportionally reduced the electric field across the blocking oxide with its dielectric constant and therefore,

electron injection from the gate during erase can be effectively suppressed which will generally in turn enhance the erase speed [54]. From the above discussion it can be concluded that HfO<sub>2</sub> and its aluminates, silicates are now the most accepted candidates. Chengyuan Yan et. al. [55] in 2019 fabricated a nonvolatile memory with a floating gate structure using ZnSe@ZnS core—shell quantum dots as discrete charge-trapping/tunneling centers. The fabricated device demonstrates a large memory window, stable retention, and good endurance. S. Wang et. al. [56] in 2019 fabricated a dual gate structure floating gate non –volatile memory device based on heterostructure of MoS<sub>2</sub> and hexagonal boron nitride. The newly introduced device exhibit long retention time, ultra low leakage current (~10<sup>-13</sup>A) and low operation voltage (~5V).

**Table 3** Work function values of various transition metals

| Element | Work function |  |  |

|---------|---------------|--|--|

|         | (eV)          |  |  |

| Pt      | 5.35          |  |  |

| Au      | 5.1           |  |  |

| Al      | 4.08          |  |  |

| Ag      | 4.0           |  |  |

| Ti      | 4.35          |  |  |

| Cr      | 4.5           |  |  |

| Fe      | 4.5           |  |  |

| Co      | 5.0           |  |  |

| Ni      | 5.01          |  |  |

| Cu      | 4.65          |  |  |

| Mg      | 3.68          |  |  |

| Nb      | 4.3           |  |  |

**Table 4** Comparison of some main properties of high-k dielectric material [53]

| Material         | Energy Gap (eV) | Conduction        | Dielectric | Crystal Structure             |

|------------------|-----------------|-------------------|------------|-------------------------------|

|                  |                 | Band offset to Si | Constant   |                               |

| SiO <sub>2</sub> | 8.9             | 3.2               | 3.9        | Amorphous                     |

| $Si_3N_4$        | 5.1             | 2                 | 7          | Amorphous                     |

| SiON             | 5.1-8.9         | 2-3.2             | 3.9-7.1    | Amorphous                     |

| $Al_2O_3$        | 8.7             | 2.8               | 9          | Amorphous                     |

| $HfO_2$          | 5.7             | 1.5               | 25         | Monoclinic, Tetragonal, Cubic |

| $ZrO_2$          | 7.8             | 1.4               | 25         | Monoclinic, Tetragonal, Cubic |

| $TiO_2$          | 3.5             | 1.2               | 80         | Tetragonal                    |

| $Ta_2O_5$        | 4.5             | 1-1.5             | 26         | Orthorhombic                  |

| $Y_2O_3$         | 5.6             | 2.3               | 15         | Cubic                         |

| $La_2O_3$        | 4.3             | 2.3               | 30         | Hexagonal, Cubic              |

#### 4. CONCLUSION

To overcome the problem of stored charge leakage back to the channel due to local defects, memory-cell structures employing discrete traps as charge storage nodes have been proposed in the past few years. Extensive researches have been conducted on non volatile memories employing metal nanocrystals/metal floating gate. Metal floating gate in combination with high-k results in good electrical characteristics even at low thicknesses and also lowers the interpoly dielectric leakage (IPD) due to larger work function. The metal nanocrystal with high work function shows enhanced charge retention time as compared to semiconductor nanocrystals and thus the high potentiality of nanocrystals for NVM applications is confirmed. The advantages of both metal NC and a high-tunneling barrier results in excellent data retention characteristic without compromising the programming efficiency and it resolve the tradeoff between programming and retention characteristic. The heterogeneous floating-gate stack of metal nanocrystals and nitride can take the better tradeoff between the programming and retention characteristics as compared to single layer of metal nanocrystals or nitride. The multilayer nanoparticle embedded nonvolatile memory contributes to additional charge storage capability and ultimately enhanced memory window. The high-k blocking oxide play vital role in the low-voltage operation and increases the coupling ratio between the control gate and metal floating gate/ metal NC layer which results in good charge storage feature. However with decrease in nanocrystal size the density of nanocrystals increases but it also faces some limitations such as high leakage density and fluctuation from device to device and isolation concept is violated. Therefore, it is indispensable to solve the scaling problem with suitable requirements in nonvolatile memory industry.

**Acknowledgement**: The author Renu organized the concept of this review paper and would like to thank Prof. Rakesh Vaid for supervising the project. Both the authors read and approved the final manuscript.

### REFERENCES

- R. Bez, E. Camerlenghi, A. Modelli and A. Visconti, "Introduction to flash memory", In Proceedings of the IEEE, 2003, vol. 91, pp. 489–502.

- [2] http://www.itrs.net/Links/2009ITRS/Home2009.htm

- [3] R. Garg, D. Misra and P. K. Swain, "Ge MOS capacitors with thermally evaporated HfO<sub>2</sub> as gate dielectric", J. of the Electrochem. Soc., vol. 153, pp. F29–F34, 2006.

- [4] A. G. Khairnar and A. M. Mahajan, "Effect of post-deposition annealing temperature on RF-sputtered HfO<sub>2</sub> thin film for advanced CMOS technology", Solid State Sci., vol. 15, pp. 24–28, 2013.

- [5] H. S. Kim, "A study of HfO<sub>2</sub>-based MOSCAPs and MOSFETs on III-V substrates with a thin germanium interfacial passivation layer", Ph.d. thesis, The University of Texas, Austin, 2008.

- [6] S. V. J. Chandra, M. Jeong, Y. C. Park, J. W. Yoon and C. J. Choi, "Effect of annealing ambient on structural and electrical properties of Ge metal-oxide-semiconductor capacitors with Pt gate electrode and HfO<sub>2</sub> gate dielectric", *Mater. Trans.*, vol. 52, pp. 118–123, 2011.

- [7] M. Saitoh, E. Nagata and T. Hiramoto, "Effects of ultra-narrow channel on characteristics of MOSFET memory with silicon nanocrystal floating gates", In Proceedings of International Electron Devices Meeting Technical Digest, 2002, pp. 181–184.

- [8] N. Konofaos, "Electrical characterisation of SiON/n-Si structures for MOS VLSI electronics", Microelectron. J., vol. 35, pp. 421–425, 2004.

- [9] I. Fainer, M. L. Kosinova, A. E. A. Macimovsky, Yu. M. Rumyantsev, F. A. Kuznetsov, V. G. Kesler, V. V. Kirienko, "Study of the structure and phase composition of nanocrystalline silicon oxynitride films synthesized by ICP-CVD", Nucl. Instrum. and Meth. in Phys. Res. Sect. A, vol. 543, pp. 134–138, 2005.

- [10] S. N. Keeney, "Dielectric scaling challenges and approaches in floating gate non-volatile memories", In Proceedings of the Electrochemical Society, 2004, vol. 04, pp. 151–158.

- [11] S. Raghunathan, T. Krishnamohan, K. Parat, and K. Saraswat, "Investigation of ballistic current in scaled floating-gate NAND FLASH and a solution", In Proceedings of the IEEE International Electron Devices Meeting, Baltimore, MD, 7-9 December, 2009, pp. 34.1.1–3.4.1.4

- [12] S. Jayanti, X. Yang, R. Suri and V. Misra, "Ultimate scalability of TaN metal floating gate with incorporation of high-k blocking dielectrics for flash memory applications", In Proceedings of the International Electron Devices Meeting, 2010, pp. 5.3.1–5.3.4

- [13] J. Brewer and M. Gill, Nonvolatile memory technologies with emphasis on flash: A comprehensive guide to understanding and using NVSM devices, IEEE, in Press: Piscataway, NJ, USA, 2008.

- [14] B. Park, K. Cho, J. Yun, Y. S. Koo, J. H. Lee, and S. Kim, "Electrical characteristics of floating-gate memory devices with titanium nanoparticles embedded in gate oxides", *J. of Nanosci. and Nanotech.*, vol. 8, pp. 1904–1908, 2008.

- [15] C. Lee, J. Meteer, V. Narayanan and E. C. Kan, "Self-Assembly of metal nanocrystals on ultrathin Oxide for nonvolatile Memory applications", J. of Electron. Mater., vol. 34 pp. 1–11, 2005.

- [16] Z. Liu, C. Lee, V. Narayanan, G. Pei and E.C. Kan, "Metal nanocrystal memories-Part I: Device design and fabrication", *IEEE Trans. on Electron Devices*, vol. 49, pp. 1606–1613, 2002.

- [17] C. Lee, T. H. Hou, and E. C. C. Kan, "Nonvolatile Memory with a metal nanocrystal/nitride heterogeneous floating-Gate", *IEEE Trans. on Electron Devices*, vol. 52, pp. 2697–2702, 2005.

- [18] S. Yamazaki, K. Hatakeyama, I. Kagawa, and Y. Yamashita, "Properties of nonvolatile semiconductor memories by using silicon clusters in the gate insulator", In Proceedings of the International Electron Devices Meeting Technical Digest, 1973, pp. 355–358.

- [19] S. Yamazaki, "Metal-insulator-semiconductor structures," Ceramic Bulletin, vol. 64, pp. 1585–1589, 1985.

- [20] R. F. Steimle, M. Sadd, R. Muralidhar, R. Rao, B. Hradsky, S. Straub and B. E. White Jr., "Hybrid silicon nanocrystal silicon nitride dynamic random access memory", *IEEE Trans. Nanotechn.*, vol. 2, pp. 335–340, 2003.

- [21] R. F. Steimle, R. A. Rao, B. Hradsky, R. Muralidhar, M. Sadd, M. Ramon, S. Straub, S. Bagchi, X. D. Wang, J. Hooker and B. E. White Jr., "Hybrid silicon nanocrystal silicon nitride memory", In Proceedings of the ICSSDM, 2003, pp. 848–849.

- [22] C. Sargentis, K. Giannakopoulos, A. Travlos and D. Tsamakis, "Fabrication and characterization of a metal nanocrystal memory using molecular beam epitaxy", J. of Phys., vol. 10, pp. 53–56, 2005.

- [23] J. J. Lee and D. L. Kwong, "Metal nanocrystal memory with high-k tunneling barrier for improved data retention," *IEEE Trans. on Electron Devices*, vol. 52, pp. 507–511, 2005.

- [24] S. M. Sze, Physics of semiconductor devices. New York: Wiley, 1981, Chapter 7.

- [25] H. Wong and H. Iwai, "On the scaling issues and high-k replacement of ultrathin gate dielectrics for nanoscale MOS transistors", *Microelectron. Eng.*, vol. 83, pp. 1867–1904, 2006.

- [26] H. Wong, B. L. Yang and Y.C. Cheng, "Chemistry of silicon oxide annealed in ammonia and its influence on interface traps", Appl. Surf. Sci., vol. 72, pp. 49–54, 1993.

- [27] E. Cartier and J. H. Stathis, "Insulating films on semiconductors", Microelectron. Eng., vol. 28, pp. 3–10, 1995.

- [28] J. T. Yount, P. M. Lenahan and J. T. Krik, "Comparison of defect structure in N<sub>2</sub>O- and NH<sub>3</sub>-nitrided oxide dielectrics", J. of Appl. Phys., vol. 76, pp. 1754–1758, 1994.

- [29] I. J. R. Baumvol, F. C. Stedile, J. J. Ganem, I. Trimaille and S. Rigo, "Thermal nitridation of SiO<sub>2</sub> films in ammonia: The role of hydrogen", J. of Electrochem. Soc., vol. 143, pp. 1426–1434, 1996.

- [30] S. Hwang, S. Jung, K. S. Jang, J. I. Lee, H. Park, S. K. Dhungel and J. Yi, "Properties of the ultra-thin silicon-oxynitride films deposited by using plasma-assisted N<sub>2</sub>O oxidation for semiconductor device applications", *J. of the Korean Phys. Soc.*, vol. 51, pp. 1096–1099, 2007.

- [31] P.H. Yeh, L.J. Chen, P.T. Liu, D.Y. Wang and T.C. Chang, "Metal nanocrystals as charge storage nodes for nonvolatile memory devices", *Electrochimica Acta* (Elsevier), vol. 52, pp. 2920–2926, 2007.

- [32] W. Guan, S. Long, R. Jia, Q. Liu, Y. Hu, Q. Wang and M. Liu, "Analysis of charge retention characteristics for metal and semiconductor nanocrystal non-volatile memories", In Proceedings of the IEEE, 2007, pp. 141.

- [33] W. Guan, S. Long, M. Liu, Z. Li, Y. Hu and Qi Liu, "Fabrication and charging characteristics of MOS capacitor structure with metal nanocrystals embedded in gate oxide", J. of Phys. D: Appl. Phys., vol. 40, pp. 2754–2758, 2007.

- [34] J. Y. Choi, E. K. Lee, Y. S. Min and J. B. Park, "Nonvolatile memory devices fabricated by using colloidal Ni nanocrystals", J. of the Korean Phys. Soc., vol. 50, pp. 49–52, 2007.

- [35] Y. Li and S. Liu, "Using different work function nanocrystal materials to improve the retention characteristics of nonvolatile memory devices", *Microelectronics J.*, vol. 40, pp. 92–94, 2009.

- [36] N. Henan, W. Liangcai, S. Zhitang, and H. Chun, "Memory characteristics of an MOS capacitor structure with double-layer semiconductor and metal heterogeneous nanocrystals", *J. of Semiconductors*, vol. 30, pp. 114003(1–5), 2009.

- [37] C. Lee, A. G. Seetharam and E. C. Kan, "Operational and reliability comparison of discrete-storage nonvolatile memories: advantages of single- and double-layer metal nanocrystals", In Proceedings of the IEDM Technical Digest, 2003, vol. 557, pp. 22.6.1–22.6.4.

- [38] Z. J. Horvath and P. Basa, "Nanocrystal non-volatile memory devices", Mater. Sci. Forum, vol. 609, pp. 1–9, 2009.

- [39] Z. J. Horvath, P. Basa, T. Jaszi, A.E. Pap, L. Dobos, B. Pecz, L. Toth, P. Szollosi and K. Nagy, "Electrical and memory properties of Si<sub>3</sub>N<sub>4</sub> MIS structures with embedded Si nanocrystals", *J. of Nanosci. and Nanotech.*, vol. 8, pp. 812–817, 2008.

- [40] P. Basa, Z. J. Horvath, T. Jaszi, A.E. Pap, L. Dobos, B. Pecz, L. Toth, and P. Szollosi, "Electrical and memory properties of Silicon nitride structures with embedded Si nanocrystals", *Phys. E: Low-Dimensional Systems and Nanostructure.*, vol. 38, pp. 71–75, 2007.

- [41] J. H. Liao, J. Y. Hsieh, H. J. Lin, W. Y. Tang, C. L. Chiang, Y. S. Lo, T. B. Wu, L. W. Yang, T. Yang, K. C. Chen and C. Y. Lu, "Physical and electrical characteristics of silicon oxynitride films with various refractive indices", *J. of Phys. D: Appl. Phys.*, vol. 42, pp. 175102(1-7), 2009.

- [42] J. S. Lee, "Recent progress in gold nanoparticle-based non-volatile memory devices", *Gold Bulletin*, vol. 43, pp. 189–199, 2010.

- [43] S. Yang, Q. Wang, M. Zhang, S. Long, J. Liu and M. Liu, "Titanium-tungsten nanocrystals embedded in a SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate dielectric stack for low-voltage operation in non-volatile memory", *Nanotechnology*, vol. 21, pp. 245201–245205, 2010.

- [44] V. Mikhelashvili, B. Meyler, S. Yofis, J. Salzman, M. Garbrecht, T. Cohen-Hyams, W. D. Kaplan, and G. Eisenstein, and Eisenstein G., "A nonvolatile memory capacitor based on a double gold nanocrystal storing layer and high-k dielectric tunneling and control layers", *J. of the Electrochem. Soc.*, vol. 157, pp. H463–H469, 2010.

- [45] G. Gay, D. Belhachemi, J. P. Colonna, S. Minoret, P. Brianceau, D. Lafond, T. Baron, G. Molas, E. Jalaguier, A. Beaurain, B. Pelissier, V. Vidal and B. De Salvo, "Passivated TiN nanocrystals/SiN trapping layer for enhanced erasing in nonvolatile memory", *Appl. Phys. Lett.*, vol. 97, pp. 152112(1–3), 2010.

- [46] L. Khomenkova, B. S. Sahu, A. Slaoui and F. Gourbilleau, "Hf-based high-k materials for Si nanocrystal floating gate memories", *Nanoscale Res. Lett.*, vol. 172, pp. 1–8, 2011.

- [47] G. X. Li, X. F. Chen, W. Ren, P. Shi, X. Q. Wu, O. K. Tan, W. G. Zhu and X. Yao, "HfO<sub>2</sub>-TiO<sub>2</sub> ultra-thin gate dielectric by RF Sputtering", Ferroelectrics, vol. 410, pp. 129–136, 2011.

- [48] M. Yun, B. Ramalingam, and S. Gangopadhyay, "Multi-layer pt nanoparticle embedded high density non-volatile memory devices", J. of the Electrochem. Soc., vol. 159, pp. H393–399, 2012.

- [49] C. T. Lin, J. C. Wang, P. W. Huang, Y. Y. Chen and L. C. Chang, "Performance revelation and optimization of gold nanocrystal for future nonvolatile memory application", *Japanese J. of Appl. Phys.*, vol. 52, pp. 04CJ09(1–5), 2013.

- [50] J. Seo, J. Y. Kim, Y. B. Kim, D. W. Kim, H. Kim, H. Jo and D. K. Choi, "Multi-level storage in a nano-floating gate MOS capacitor using a stepped control oxide", *Microelectron. Reliability*, vol. 53, pp. 528–532, 2013.

- [51] W. C. Shih, C. H. Cheng, J. Y. M. Lee and F. C. Chiu "Charge-trapping devices using multilayered dielectrics for nonvolatile memory applications", Advances in Mater. Sci. and Eng., pp.1–5, 2013.

- [52] G. Chen, Z. Huo, L. Jin, Y. Han, X. Li, Su Liu and M. Liu, "Metal floating gate memory device with SiO<sub>2</sub>/HfO<sub>2</sub> dual-layer as engineered tunneling barrier", *IEEE Electron Device Lett.*, vol. 35, pp. 744–746, 2014.

- [53] G. D. Wilk, R. M. Wallace and J. M. Anthony, "H-k gate dielectrics: current status and materials properties considerations", J. of Appl. Phys., vol. 89, pp. 5243–5255, 2001.

- [54] C. Zhao, C. Z. Zhao, S. Taylor and P. R. Chalker, "Review on non-volatile memory with High-k dielectrics: Flash for generation beyond 32 nm", *Mater.*, vol. 7, pp. 5117–5145, 2014.

- [55] C. Yan, J. Wen, P. Lin and Z. Sun, "A tunneling dielectric layer free floating gate nonvolatile memory employing type-i core–shell quantum dots as discrete charge-trapping/tunneling centers", *Nano-Micro Small*, vol.15, pp.1804156 (1–8), 2019.

- [56] S. Wang, C. He, J. Tang, X. Lu, C. Shen, H. Yu, L. Du, J. Li, R. Yang, D. Shi and G. Zhang, "New floating gate memory with excellent retention characteristics", *Advanced Electron. Mater.*, vol. 5, pp. 1800726 (1–7), 2019.