# Comparison of Pulse Width Modulation Techniques for Diode-Clamped and Cascaded Multilevel Inverters

## **Kishor Gudipati**

E.E.E Department, G.Pulla Reddy Engineering College, India gudipatikishor@gmail.com (corresponding author)

## Harsha Vardhan Reddy Maramreddy

E.E.E Department, G.Pulla Reddy Engineering College, India maramreddyharsha@gmail.com

## Sri Gowri Kolli

E.E.E Department, G.Pulla Reddy Engineering College, India gowrivasu.3@gmail.com

## Vuyyuru Anantha Lakshmi

E.E.E Department, G.Pulla Reddy Engineering College, India v.al@rediffmail.com

## Girireddy Sreenivasa Reddy

E.E.E Department, G.Pulla Reddy Engineering College, India nivasa7hills@gmail.com

Received: 11 April 2023 | Revised: 29 April 2023 | Accepted: 5 May 2023

Licensed under a CC-BY 4.0 license | Copyright (c) by the authors | DOI: https://doi.org/10.48084/etasr.5939

#### ABSTRACT

Multilevel inverter technology has become the most significant method of energy conversion from DC to AC for uninterrupted power supply. The quality of the power supply depends on the appearance of harmonics, which is considered a problem that needs to be overcome. This paper demonstrates the use of a new modulation technique to reduce the harmonics in both diode-clamped and cascaded multilevel inverters, examining its Total Harmonic Distortion (THD) compared to other PWM methods. Simulations were carried out in MATLAB/Simulink for five-level diode-clamped and cascaded multilevel inverters. The simulation results of both multilevel inverters using the sinusoidal PWM, modified reference PWM, modified carrier PWM, and modified reference and modified carrier PWM methods showed that the latter had the best THD performance for both inverter types, especially for the cascaded multilevel inverter.

Keywords-Harmonics; Multi Level Inverter (MLI); Pulse Width Modulation (PWM)

#### I. INTRODUCTION

The rapidly expanding field of multilevel power conversion technology in power electronics offers great potential for development. A new breed of multilevel inverters has emerged as a possible alternative to handle high voltage levels. The appropriate multilevel inverter for each application is not always obvious, as it depends on several agile methodologies. Multilevel inverters (MLIs) bring the output waveform closer to a sinusoidal waveform, minimizing Total Harmonic Distortion (THD). Core inverter designs include flying capacitor cascaded and diode-clamped circuits to get beyond the solid-state switching device rating restrictions and facilitate the adoption of multilevel inverter topologies in higher-voltage systems. A design feature of multiple voltage source inverters enables them to achieve high voltages with low harmonics without relying on transformers. The primary function of a multilayer inverter is to combine many layers of DC voltages to produce the desired AC voltage. Table I shows that to accomplish the same number of voltage levels, inverters need an equal number of main switches and main diodes. As cascaded inverters do not require clamping diodes, they have the smallest component count [1-12].

| Engineering, Technology & Applied Science Researc | Engin | eering, | Technology | & Applied | Science | Research |

|---------------------------------------------------|-------|---------|------------|-----------|---------|----------|

|---------------------------------------------------|-------|---------|------------|-----------|---------|----------|

| Types of switches      | Diode<br>clamped MLI | Capacitor<br>clamped MLI | Cascaded<br>MLI |

|------------------------|----------------------|--------------------------|-----------------|

| Clamping diodes        | (n-1)*(n-2)          | 0                        | 0               |

| Balancing capacitors   | 0                    | (n-1)*(n-2)/2            | 0               |

| Main diodes            | 2(n-1)               | 2(n-1)                   | 2(n-1)          |

| DC bus capacitors      | (n-1)                | (n-1)                    | (n-1)/2         |

| Main switching devices | 2(n-1)               | 2(n-1)                   | 2(n-1)          |

TABLE I. SWITCHES FOR DIFFERENT MULTILEVEL INVERTERS

#### II. DIFFERENT MULTILEVEL TECHNIQUES

#### A. Diode Clamped Inverter (DCMLI)

In a DCMLI, the diode acts as the clamping device to reach stages in the o/p voltage, which makes it a unique MLI when compared with other topologies. In an *m*-level diode-clamped inverter, the voltage over each capacitor is  $V_{dc}/m$ -1. The phases are connected to a number of capacitors via the diode-clamped inverter, which produces multiple voltage levels, whether or not each action-switching device prevents  $V_{dc}/m$ -1 [13-23].

## B. Cascaded Multilevel Inverter (CDMLI)

The flexibility of this arrangement facilitates maintenance and provides a straightforward method of system redundancy. CDMLI is a combination of *H*-bridges that are connected in series. An *N*-level *H*-bridge MLI has two (*N*-1)/2 switches, which are series-connected phases. A single phase makes up each cell. Therefore, the requirement is four active switches in each cell, which can generate three voltage levels: 0, *Vdc*/2, and -Vdc/2. Attaching all cells in a cascade will result in voltage stages, with the cell voltages added together making up the phase voltage  $V_{an}=V_1+V_2+V_3+...+V_n$  [24-31].

## III. DIFFERENT MODULATION TECHNIQUES

There are several different types of modulation techniques to generate pulses to trigger the switches of an inverter.

### A. Sinusoidal Pulse Width Modulation (SPWM)

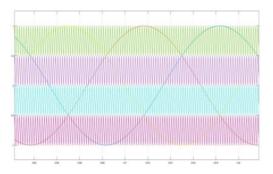

In SPWM, a high switching frequency carrier wave signal, i.e., a triangular wave signal, is compared with the reference sinusoidal signal.

Fig. 1. Sinusoidal reference comparison with normal triangular waves.

SPWM modulates one sinusoidal signal with many triangular carrier signals [32-46]. The carriers' peak-to-peak amplitudes  $(A_c)$  and frequencies  $(F_c)$  are identical. The zero references of the carrier set are situated in the middle. A switch

is triggered if the modulating signal is greater than the triangle carrier assigned to it [47].

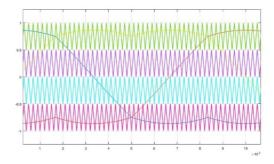

## B. Modified Reference Pulse Width Modulation (MRPWM)

In the general sinusoidal PWM approaches, for example at 2-level inverters, every phase voltage is set parallel to that of the triangular carrier signal, to generate the voltages [48]. To get the maximum of the common-mode voltage,  $V_{offsetl}$  is connected to the phase voltages [49-50], therefore:

$$V_{offset1} = \frac{-(V_{max} + V_{min})}{2} \tag{1}$$

While a reference phase voltage is measured throughout a sample, three recommended phase voltages are measured within a sampling time.  $V_{max}$  is the voltage at the maximum point and  $V_{min}$  is the voltage at the minimum point. When the commons mode voltage,  $V_{offsetl}$ , is included, the effective inverter switching vectors are minimal in a sample period.

Fig. 2. Modified reference comparison with normal triangular waves.

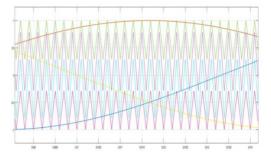

C. Modified Carrier Pulse Width Modulation (MCPWM)

Figure 3 shows the carrier vertical offset for MLI using the modified carrier technique.

Fig. 3. Sinusoidal reference comparison with modified carrier waves.

The source sine wave is positioned in the center of the four triangular carriers, which can be observed to be overlapped. Each triangular wave is compared with the reference signal and, hence, the triggering pulses are generated.

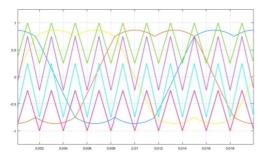

## D. Modified Reference and Modified Carrier Pulse Width Modulation (MRCPWM)

Figure 4 shows the carrier vertical offset MLI using the modified reference and modified carrier technique. The four carriers may be observed to be overlapping, and a modified sine wave (or third harmonic wave) is positioned in the middle of the four. Each triangular wave is compared with the reference signal and, hence, the triggering pulses are generated.

Fig. 4. Modified reference comparison with modified carrier waves.

## IV. SIMULATION RESULTS FOR DIODE-CLAMPED MLI

## A. Sinusoidal PWM (SPWM)

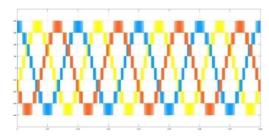

Figures 5 and 6 show the line voltages and the FFT analysis obtained from a diode-clamped five-level inverter using the SPWM technique to trigger its switches. The obtained THD percentage was 18.09%.

Fig. 5. Line voltages of diode-clamped MLI with SPWM.

Fig. 6. FFT analysis of diode-clamped MLI with SPWM.

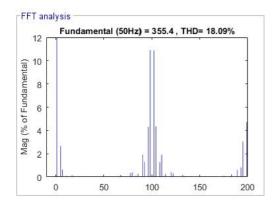

#### B. Modified Reference PWM (MRPWM)

Figures 7 and 8 show the line voltages and the FFT analysis obtained from a diode-clamped five-level inverter using the MRPWM technique to trigger its switches. The obtained THD was 13.20%, which was lower than the obtained for the same inverter with SPWM.

Vol. 13, No. 4, 2023, 11078-11084

Fig. 7. Line voltages of diode-clamped MLI with MRWM.

Fig. 8. FFT analysis diode-clamped MLI with MRWM.

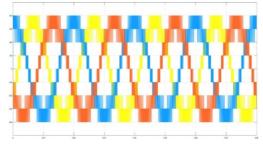

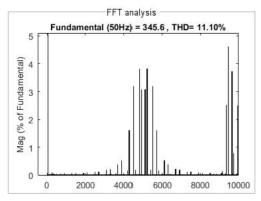

## C. Modified Carrier PWM (MCPWM)

Figures 9 and 10 show the line voltages and the FFT analysis obtained from the diode-clamped five-level inverter using the MCPWM technique to trigger its switches. The obtained THD was 11.10%, which was lower than those obtained for the same MLI type with SPWM and MRPWM.

Fig. 9. Line voltages of diode-clamped MLI with MCPWM.

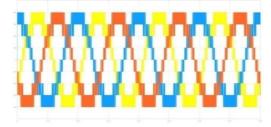

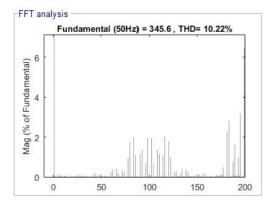

## D. Modified Reference and Modified Carrier PWM (MRMCPWM)

Figures 11 and 12 show the line voltages and the FFT analysis obtained from the diode-clamped five-level inverter using the MRMCPWM technique to trigger its switches. The obtained THD was 10.22%, which was lower than those obtained for the same type of MLI with the other techniques.

#### V. SIMULATION RESULTS FOR CASCADED MLI

#### A. Sinusoidal PWM (SPWM)

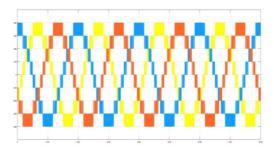

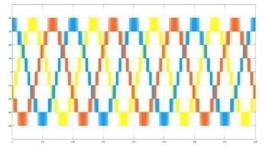

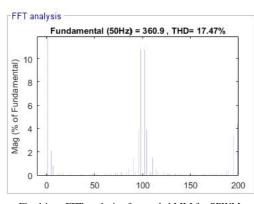

Figures 13 and 14 show the line voltages and the FFT analysis obtained for the cascaded five-level inverter using the

SPWM technique to trigger its switches. The percentage of THD obtained was 17.47%. As this PWM technique for the diode-clamped MLI obtained 18.09% THD, this technique worked better for cascaded MLI.

Fig. 10. FFT analysis of diode-clamped MLI with MCPWM.

Fig. 11. Line voltages of diode-clamped MLI with MRMCPWM.

Fig. 12. FFT analysis of diode-clamped MLI with MRMCPWM.

Fig. 13. Line voltages of cascaded MLI for SPWM.

Fig. 14. FFT analysis of cascaded MLI for SPWM.

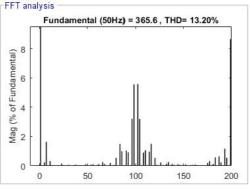

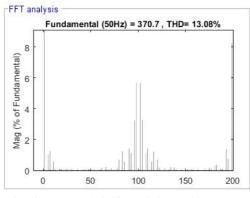

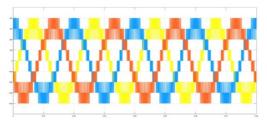

#### B. Modified Reference PWM (MRPWM)

Figures 15 and 16 show the line voltages and the FFT analysis obtained for the cascaded five-level inverter using the MRPWM technique to trigger its switches. The THD obtained was 13.08%, showing that this technique also worked better for cascaded MLI.

Fig. 15. Line voltages of cascaded MLI with MRPWM.

Fig. 16. FFT analysis of cascaded MLI with MRPWM.

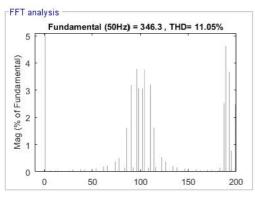

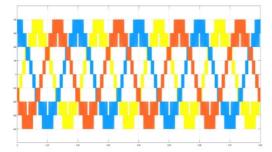

#### C. Modified Carrier PWM (MCPWM)

Figures 17 and 18 show the line voltages and the FFT analysis obtained for the cascaded five-level inverter using the MCPWM technique to trigger its switches. The THD obtained was 11.05%.

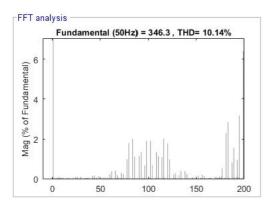

## D. Modified Reference and Modified Carrier PWM (MRMCPWM)

Figures 19 and 20 show the line voltages and the FFT analysis obtained for the cascaded five-level inverter using the

MRMCPWM technique to trigger its switches. The THD obtained was 10.14%, which is smaller compared to the result when using the same PWM technique for the diode-clamped MLI. Therefore, this technique works better for cascaded MLI.

Fig. 17. Line voltages of cascaded MLI with MCPWM.

Fig. 18. FFT analysis of cascaded MLI with MCPWM.

Fig. 19. Line voltages of cascaded MLI with MRMCPWM.

Fig. 20. FFT analysis of cascaded MLI with MRMCPWM.

VI.

Table II demonstrates the performance of the diodeclamped multilevel inverter in terms of THD using the SPWM, MRPWM, MCPWM, and MRCPWM techniques. This table clearly shows that of all the mentioned PWM techniques, the MRCPPWM technique worked better, as its THD percentage was lower. The lower the THD percentage, the higher the quality of power delivered by the inverter.

| TABLE II. | DCMLI THD RESULTS |

|-----------|-------------------|

|           |                   |

| DCMLI (Diode Clamped Multilevel inverter) |                              |                  |                 |                  |

|-------------------------------------------|------------------------------|------------------|-----------------|------------------|

| Switching<br>frequency(Hz)                | Sinusoidal<br>PWM<br>(% THD) | MRPWM<br>(% THD) | MCPWM<br>(%THD) | MRCPWM<br>(%THD) |

| 1KHz                                      | 23.54                        | 18.40            | 16.2            | 14.13            |

| 5KHz                                      | 20.01                        | 15.14            | 13.0            | 11.12            |

| 10KHz                                     | 18.09                        | 13.20            | 11.1            | 10.22            |

Table III demonstrates the performance of cascaded MLI in terms of THD using SPWM, MRPWM, MCPWM, and MRCPWM. This table clearly shows that of all the mentioned PWM techniques, the MRMCPWM worked the best, as its THD percentage was lower for the cascaded MLI. The cascaded MLI is a widely used inverter where a small decrease in its THD makes the inverter suitable for wide applications. The power quality obtained by lowering the THD percentage in cascaded MLI can fill the gap in many power quality issues.

TABLE III. CDMLI(CASCADED MULTILEVEL INVERTER)

| CDMLI (Cascaded Multilevel inverter) |                              |                  |                  |                   |

|--------------------------------------|------------------------------|------------------|------------------|-------------------|

| Switching<br>frequency(Hz)           | Sinusoidal<br>PWM<br>(% THD) | MRPWM<br>(% THD) | MCPWM<br>(% THD) | MRCPWM<br>(% THD) |

| 1KHz                                 | 23.00                        | 18.30            | 16.0             | 13.92             |

| 5KHz                                 | 19.89                        | 14.52            | 12.7             | 11.01             |

| 10KHz                                | 17.47                        | 13.08            | 11.0             | 10.14             |

Table IV demonstrates the THD of both the cascaded multilevel and the diode-clamped inverters using MRMCPWM. The results show that the MRMCPWM is the best PWM technique compared to conventional PWM techniques. Moreover, the higher the switching frequency, the lower the harmonics were observed for both inverter topologies. The lower harmonics in the power supply improved power quality, which affects the torque produced in motor drives. Furthermore, the efficiency and life span of any motor drive is directly proportional to the quality of the power supplied to it.

TABLE IV.

MODIFIED REFERENCE AND MODIFIED CARRIER PWM (MRCPWM)

| Switching<br>frequency(Hz) | Diode clamped MLI<br>(THD in %) | Cascaded MLI<br>(THD in %) |

|----------------------------|---------------------------------|----------------------------|

| 1KHz                       | 13.92                           | 13.45                      |

| 5KHz                       | 11.12                           | 11.01                      |

| 10KHz                      | 10.22                           | 10.14                      |

It should be noted that for both inverters with different PWM techniques, a resistive load of  $10\Omega$  was taken, the modulation index was 0.8, and the DC link voltage was 400V.

#### VII. CONCLUSION

This study presented the harmonic spectrum for cascade and diode-clamped 3-phase 5-level inverters using the SPWM, MRPWM, MCPWM, and MRMCPWM techniques. A comparison of these techniques for both inverters showed that MRCPWM provided a spectrum that is tolerant for application, especially for the cascaded MLI inverter. Therefore, for any five-level inverter application, it is recommended to use the MRCPWM technique as its THD percentage is significantly lower.

#### REFERENCES

- G. Kishor, Maramreddy Harsha Vardhan Reddy, and Repalle Rohit, "Performance Evaluation of Five-Level DCMLI and Cascaded MLI By using PWM Techniques," *International Journal of Early Childhood* Special Education, vol. 14, no. 04, 2022.

- [2] R. Jadeja, A. Ved, and S. Chauhan, "An Investigation on the Performance of Random PWM Controlled Converters," *Engineering*, *Technology & Applied Science Research*, vol. 5, no. 6, pp. 876–884, Dec. 2015, https://doi.org/10.48084/etasr.599.

- [3] B. A. Nasir, "Determination of the Harmonic Losses in an Induction Motor Fed by an Inverter," *Engineering, Technology & Applied Science Research*, vol. 12, no. 6, pp. 9536–9545, Dec. 2022, https://doi.org/10.48084/etasr.5012.

- [4] Y. Gopal, K. P. Panda, D. Birla, and M. Lalwani, "Swarm Optimization-Based Modified Selective Harmonic Elimination PWM Technique Application in Symmetrical H-Bridge Type Multilevel Inverters," *Engineering, Technology & Applied Science Research*, vol. 9, no. 1, pp. 3836–3845, Feb. 2019, https://doi.org/10.48084/etasr.2397.

- [5] G. Kishor, M. H. V. Reddy, R. Ramprasad, and S. J. Vali, "A Single Core Double Inductor Buck-Boost Converter with Positive Output Voltage," *International Journal of Recent Technology and Engineering*, vol. 7, no. 6s, pp. 393–398, 2019.

- [6] M. H. V. Reddy, T. B. Reddy, B. R. Reddy, and M. Suryakalavathi, "Reduction of Common Mode Voltage in Asymmetrical Dual Inverter Configuration Using Discontinuous Modulating Signal Based PWM Technique," *Journal of Power Electronics*, vol. 15, no. 6, pp. 1524– 1532, 2015, https://doi.org/10.6113/JPE.2015.15.6.1524.

- [7] M. H. V. Reddy, K. S. Gowri, T. B. Reddy, and G. Kishor, "Effect of center voltage vectors (CVVs) of three-level space plane on the performance of dual inverter fed open end winding induction motor drive," *Chinese Journal of Electrical Engineering*, vol. 5, no. 2, pp. 43– 55, Jun. 2019, https://doi.org/10.23919/CJEE.2019.000010.

- [8] K. S. Gowri, M. H. V. Reddy, G. Kishor, T. B. Reddy, and T. Jagadeesh, "Three Phase Space Vector PWM Based Multilevel Inverter for Pumping Applications," *TEST Engineering & Management*, vol. 82, pp. 8696–8705, Jan. 2020.

- [9] B. Kaku, I. Miyashita, and S. Sone, "Switching loss minimised space vector PWM method for IGBT three-level inverter," *IEE Proceedings -Electric Power Applications*, vol. 144, no. 3, pp. 182–190, May 1997, https://doi.org/10.1049/ip-epa:19970989.

- [10] Gudipati Kishor, Maramreddy Harsha Vardhan Reddy, and Repalle Rohit, "Performance Evaluation of Five-Level DCMLI and Cascaded MLI By using PWM Techniques," *International Journal of Early Childhood Special Education*, vol. 14, no. 4, 2022.

- [11] Maramreddy Harsha Vardhan Reddy, Gudipati Kishor, and Repalle Rohi, "Optimization of Diode-Clamped Multilevel Inverter by Using Switching Losses and THD," vol. 14, no. 4, pp. 9–20, 2022.

- [12] A. M. Hava, R. J. Kerkman, and T. A. Lipo, "Simple analytical and graphical methods for carrier-based PWM-VSI drives," *IEEE Transactions on Power Electronics*, vol. 14, no. 1, pp. 49–61, Jan. 1999, https://doi.org/10.1109/63.737592.

- [13] G. Kishor, D. Subbarayudu, and S. Sivanagaraju, "Experimental Investigations on Two InductorBoost Converter System," *International Journal of Computer and Electrical Engineering*, vol. 3, no. 1, pp. 158– 162, 2011, https://doi.org/10.7763/IJCEE.2011.V3.307.

- [14] G. Kishor, D. Subbarayudu, and S. Sivanagaraju, "Digital Implementation of Two Inductor Boost Converter Fed DC Drive," *Research Journal of Applied Sciences, Engineering and Technology*, vol. 3, no. 1, pp. 39–45, 2011.

- [15] G. Kishor, D. Subbarayudu, and S. Sivanagaraju, "Comparison of Full Bridge and two Inductor Boost Converter Systems," *Journal of Theoretical and Applied Information Technology*, vol. 34, no. 2, pp. 118–124, 2005.

- [16] K. V. Kumar and G. Kishor, "Digital Simulation of Power Converter and it's Control in Microgrid," *International Journal of Soft Computing and Engineering*, vol. 3, no. 4, pp. 98–102, 2013.

- [17] C. S. Mubeen and G. Kishor, "Digital Simulation Of Current Fed Quasi -Z Source Inverter," *International Journal of Engineering Research and Applications*, vol. 3, no. 4, pp. 2382–2388, 2013.

- [18] P. H. Varsha and G. Kishor, "PWM Techniques for three Phase Rectifiers," *International Journal of Engineering Research and Management*, vol. 01, no. 07, pp. 166–168, Oct. 2014.

- [19] S. Renuka and K. G., "Non-Conventional Multi-level Inverter with Reduced Number of Voltage Sources and Switches," *International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering*, vol. 3, no. 5, pp. 207–210, May 2015, https://doi.org/10.17148/IJIREEICE.2015.3550.

- [20] K. B. Rajeswari, G. S. Reddy, G. Satheesh, and G. Kishor, "Modified Three Phase VSI with Generalized Pulse Width Modulation," *International Journal of Advanced Information and Communication Technology*, vol. 2, no. 5, 2015.

- [21] B. V. Vani, G. Satheesh, G. Kishor, and R. Rampasad, "Space Vector based Transistor-Clamped Cascaded Multilevel Inverter," *International Journal of Advanced Information and Communication Technology*, vol. 2, no. 5, 2015.

- [22] L. D. S, R. S. Kumar, and K. G, "Enhancement of a power quality by Shunt Active Power Filters Using Intelligence Techniques.," *International Journal for Research in Science Engineering & Technology*, vol. 1, no. 1, pp. 13–18, 2014, https://doi.org/10.5281/ijrset.v1i1.51.

- [23] P SIVA Deepthi, B. Gururaj, G. Kishore, and K. N. Achari, "A Novel Matlab/Simelectronics Model of PV Array with MPPT Controller," *International Journal of Electronics and Electical Engineering*, vol. 2, no. 3, Sep. 2020, https://doi.org/10.47893/IJEEE.2014.1089.

- [24] G. Kishor, K. Bee, and S. Kumar, "A Simple Circuit For The Generation Of High Voltage DC from AC by using Ladder Network," *International Journal Of Core Engineering & Managemen*, vol. 1, Special Issue, pp. 170–177, Dec. 2015.

- [25] G. Kishor, B. Ganesh, and M. Prasad, "A Case Study on Power Consumption Based on Illumination Techniques," *International Journal Of Core Engineering & Managemen*, vol. 1, Special Issue, pp. 184–192, Dec. 2015.

- [26] G. Kishor, M. H. V. Reddy, and K. Pushpalatha, "Performance investigation of 3z buck boost converter for renewable applications," *International Journal of Engineering & Technology*, vol. 7, no. 3.29, pp. 352–359, 2018.

- [27] G. Kishor and R. Ramprasad, "Fuzzy Control for Speed Control of DC Motor with Two-inductor Boost Converter," *Trends in Electrical Engineering*, vol. 8, no. 2, pp. 1–9, Oct. 2018, https://doi.org/10.37591/.v8i2.891.

- [28] M. Harshavarshan Reddy, G. Kishor, G. Satheesh, and T. Bramhananda Reddy, "Digital simulation of hybrid PWM inverter fed induction motor using two inductor boost converter," in *IEEE-International Conference On Advances In Engineering, Science And Management (ICAESM -*2012), Nagapattinam, India, Mar. 2012, pp. 361–366.

- [29] M. Mahbub and M. A. Hossain, "Design, Simulation and Comparison of Three-phase Symmetrical Hybrid Sinusoidal PWM fed Inverter with Different PWM Techniques," in 2021 2nd International Conference on Robotics, Electrical and Signal Processing Techniques (ICREST), Dhaka, Bangladesh, Jan. 2021, pp. 1–5, https://doi.org/10.1109/ ICREST51555.2021.9331086.

- [30] K. Chenchireddy and V. Jegathesan, "Multi-Carrier PWM Techniques Applied to Cascaded H-Bridge Inverter," in 2022 International

Conference on Electronics and Renewable Systems (ICEARS), Tuticorin, India, Mar. 2022, pp. 244–249, https://doi.org/10.1109/ICEARS53579 .2022.9752442.

- [31] S. Jain, N. Kishore, and K. Shukla, "Comparison of Various PWM Techniques for DC Link Capacitors Voltage Balancing of a Three-Level NPC VSI," in 2022 IEEE 10th Power India International Conference (PIICON), New Delhi, India, Aug. 2022, pp. 1–5, https://doi.org/10.1109/PIICON56320.2022.10045306.

- [32] G. Narayanan and V. T. Ranganathan, "Triangle-Comparison Approach and Space Vector Approach to Pulsewidth Modulation in Inverter fed Drives," *Journal of the Indian Institute of Science*, vol. 80, pp. 409–427, Oct. 2000.

- [33] E. R. C. da Silva, E. C. dos Santos, and B. Jacobina, "Pulsewidth Modulation Strategies," *IEEE Industrial Electronics Magazine*, vol. 5, no. 2, pp. 37–45, Jun. 2011, https://doi.org/10.1109/MIE.2011.941120.

- [34] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," *IEEE Transactions on Industrial Electronics*, vol. 49, no. 4, pp. 724–738, Dec. 2002, https://doi.org/10.1109/TIE.2002.801052.

- [35] G. P. Adam, S. J. Finney, A. M. Massoud, and B. W. Williams, "Capacitor Balance Issues of the Diode-Clamped Multilevel Inverter Operated in a Quasi Two-State Mode," *IEEE Transactions on Industrial Electronics*, vol. 55, no. 8, pp. 3088–3099, Dec. 2008, https://doi.org/10.1109/TIE.2008.922607.

- [36] E. G. Shivakumar, K. Gopakumar, S. K. Sinha, A. Pittet, and V. T. Ranganathan, "Space vector PWM control of dual inverter fed open-end winding induction motor drive," in *APEC 2001. Sixteenth Annual IEEE Applied Power Electronics Conference and Exposition (Cat. No.01CH37181)*, Mar. 2001, vol. 1, pp. 399–405 vol.1, https://doi.org/10.1109/APEC.2001.911678.

- [37] V. T. Somasekhar, E. G. Shivakumar, K. Gopakumar, and A. Pittet, "Multi Level Voltage Space Phasor Generation for an Open-End Winding Induction Motor Drive Using a Dual Inverter Scheme with Asymmetrical DC-Link Voltages," *EPE Journal*, vol. 12, no. 3, pp. 59– 77, Aug. 2002, https://doi.org/10.1080/09398368.2002.11463508.

- [38] B. V. Reddy and V. T. Somasekhar, "A Dual Inverter Fed Four-Level Open-End Winding Induction Motor Drive With a Nested Rectifier-Inverter," *IEEE Transactions on Industrial Informatics*, vol. 9, no. 2, pp. 938–946, Feb. 2013, https://doi.org/10.1109/TII.2012.2223224.

- [39] B. P. McGrath and D. G. Holmes, "Multicarrier PWM strategies for multilevel inverters," *IEEE Transactions on Industrial Electronics*, vol. 49, no. 4, pp. 858–867, Dec. 2002, https://doi.org/10.1109/ TIE.2002.801073.

- [40] D. Banerjee, R. Ghosh, G. Narayanan, and V. T. Ranganathan, "Comparison of various sine-triangle PWM techniques for three level voltage source inverters in space vector domain," in *Proceedings of NPEC IIT*, Kharagpur, India, Dec. 2005.

- [41] W. Yao, H. Hu, and Z. Lu, "Comparisons of Space-Vector Modulation and Carrier-Based Modulation of Multilevel Inverter," *IEEE Transactions on Power Electronics*, vol. 23, no. 1, pp. 45–51, Jan. 2008, https://doi.org/10.1109/TPEL.2007.911865.

- [42] I. Pereira and A. Martins, "Multicarrier and space vector modulation for three-phase NPC converters: A comparative analysis," in 2009 13th European Conference on Power Electronics and Applications, Barcelona, Spain, Sep. 2009, pp. 1–10.

- [43] E. G. Shivakumar, V. T. Somasekhar, K. K. Mohapatra, K. Gopakumar, L. Umanand, and S. K. Sinha, "A multi level space phasor based PWM strategy for an open-end winding induction motor drive using two inverters with different DC link voltages," in 4th IEEE International Conference on Power Electronics and Drive Systems. IEEE PEDS 2001 - Indonesia. Proceedings (Cat. No.01TH8594), Denpasar, Indonesia, Jul. 2001, vol. 1, pp. 169–175 vol.1, https://doi.org/10.1109/ PEDS.2001.975306.

- [44] V. T. Somasekhar, E. G. Shivakumar, K. Gopakumar, and A. Pittet, "Multi Level Voltage Space Phasor Generation for an Open-End Winding Induction Motor Drive Using a Dual Inverter Scheme with Asymmetrical DC-Link Voltages," *EPE Journal*, vol. 12, no. 3, pp. 59– 77, Aug. 2002, https://doi.org/10.1080/09398368.2002.11463508.

- [45] S. Lakhimsetty, N. Surulivel, and V. T. Somasekhar, "Improvised SVPWM Strategies for an Enhanced Performance for a Four-Level Open-End Winding Induction Motor Drive," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 4, pp. 2750–2759, Apr. 2017, https://doi.org/10.1109/TIE.2016.2632059.

- [46] M. H. V. Reddy, T. B. Reddy, B. R. Reddy, and M. S. Kalavathi, "Discontinuous PWM Technique for the Asymmetrical Dual Inverter Configuration to Eliminate the Overcharging of DC-Link Capacitor," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 1, pp. 156– 166, Jan. 2018, https://doi.org/10.1109/TIE.2017.2716858.

- [47] B. Urmila and R. Rohit, "Performance evaluation of multilevel inverter based on total harmonic distortion (THD)," *International journal of engineering science & advanced technology*, vol. 2, no. 3, pp. 587–593, 2012.

- [48] J. S. Kim and S. K. Sul, "A Novel Voltage Modulation Technique of the Space Vector PWM," *IEEJ Transactions on Industry Applications*, vol. 116, no. 8, pp. 820–825, 1996, https://doi.org/10.1541/ieejias.116.820.

- [49] J. Holtz, "Pulsewidth modulation-a survey," *IEEE Transactions on Industrial Electronics*, vol. 39, no. 5, pp. 410–420, Jul. 1992, https://doi.org/10.1109/41.161472.

- [50] R. Teodorescu *et al.*, "Multilevel Converters: Multilevel Converters," in *EPE'99 : European Conference on Power Electronics and Applications*, Lausanne, Switzerland, Sep. 1999.