## Numerical Simulation of Nanoscale Double-Gate MOSFETs

R. Stenzel, L. Müller, T. Herrmann, W. Klix

The further improvement of nanoscale electron devices requires support by numerical simulations within the design process. After a brief description of our SIMBA 2D/3D-device simulator, the results of the simulation of DG-MOSFETs are represented. Starting from a basic structure with a gate length of 30 nm, the model parameters were calibrated on the basis measured values from the literature. Afterwards variations in of gate length, channel thickness and doping, gate oxide parameters and source/drain doping were made in connection with numerical calculation of the device characteristics. Then a DG-MOSFET with a gate length of 15 nm was optimized. The optimized structure shows suppressed short channel behavior and short switching times of about 0.15 ps.

Keywords: Device simulation, semiconductor devices, double-gate MOSFET.

### **Notation**

| p, n                                  | hole and electron density (cm <sup>-3</sup> )                          |

|---------------------------------------|------------------------------------------------------------------------|

| $\varphi$                             | electrostatic potential (V)                                            |

| $N_{\rm A}, N_{ m D}$                 | ionized donor and acceptor density (cm <sup>-3</sup> )                 |

| $\varepsilon_{\mathrm{s}}$            | permittivity of semiconductor (AsV <sup>-1</sup> m <sup>-1</sup> )     |

| q                                     | elementary charge (As)                                                 |

| $J_{ m p}$ , $J_{ m n}$               | current densities (Acm <sup>-2</sup> )                                 |

| R, G                                  | recombination and generation rate (cm <sup>-3</sup> s <sup>-1</sup> )  |

| $\mu_{\rm p}, \mu_{\rm n}$            | carrier mobilities (cm <sup>2</sup> V <sup>-1</sup> cm <sup>-1</sup> ) |

| $\lambda_{\rm p}$ , $\lambda_{\rm n}$ | quantum correction potentials (V)                                      |

| $\Theta_{\rm p}, \Theta_{\rm n}$      | band parameters (V)                                                    |

| $D_{\rm p}$ , $D_{\rm n}$             | diffusion coefficients (cm <sup>2</sup> s <sup>-1</sup> )              |

| $T_{\rm p}$ , $T_{\rm n}$             | carrier temperatures (K)                                               |

| $k_{\rm B}^{'}$                       | Boltzmann constant (eVK <sup>-1</sup> )                                |

| $S_{\rm p}, S_{\rm n}$                | energy flux densities (Wcm <sup>-2</sup> )                             |

| $\boldsymbol{E}$                      | electric field strength (Vcm <sup>-1</sup> )                           |

| $T_{ m L}$                            | lattice temperature (K)                                                |

| $\tau_{ m wp}, \tau_{ m wn}$          | energy relaxation times (s)                                            |

| $m_{\rm p}, m_{\rm n}$                | carrier effective masses (kg)                                          |

| $\hbar$                               | reduced Planck's constant (Js)                                         |

| $\gamma_{\rm p}, \gamma_{\rm n}$      | quantum correction coefficient                                         |

| $\kappa_{\rm p}, \kappa_{\rm n}$      | thermal conductivities (WK <sup>-1</sup> cm <sup>-1</sup> )            |

### 1 Introduction

Double-Gate (DG) MOSFETs are considered to be a promising candidate for nanoscale CMOS. The International Technology Roadmap for Semiconductors (2005 Edition) predicts printed gate lengths up to 15 nm for the next ten years. For these gate lengths conventional MOSFETs are limited due to different short channel effects. On the other hand structures with two gates and an extremely thin body demonstrate better control of the gate region and consequently suppression of short channel effects.

Numerical device simulation is an important procedure for the design and optimization of novel semiconductor devices. Some advantages are that the electrical behavior iscalculated before the fabrication process, non-measurable inner-electronic values can be calculated and visualizated, and cost effectiveness due to diagnosis/fault-detection in the technological process.

#### 2 Simulation models

Quantum hydrodynamic (QHD) models, which are based on a quantum fluid dynamic model, offer new ways to understand and design quantum sized semiconductor devices. The advantage of this model is its macroscopic character, which enables us obtain description without knowing of quantum mechanical details like the initial wave function [1], [2], [3]. The classical hydrodynamic (HD) model for semiconductor device simulation can be extended by expressions in the transport equations and in the energy balance equations. These describe an internal quantum potential in the transport equation as well as a quantum heat flux in the energy balance equation. These additional terms in the classical hydrodynamic model allow us to describe the continuous electron and hole distribution in a semiconductor device, accumulations of carriers in potential wells and resonant tunneling of carriers, respectively. The standard model for universal device simulations is the drift-diffusion (DD) model, which can be derived from the above mentioned model [4].

Basic equations of the QHD model are the Poisson equation

$$\nabla (\varepsilon_{s} \nabla (\varphi)) = -q (p - n + N_{D} - N_{A}) \tag{1}$$

continuity equations (index p: holes, index n: electrons)

$$\nabla \cdot \boldsymbol{J}_{p} = -q \left( R - G + \frac{\partial p}{\partial t} \right) \tag{2}$$

$$\nabla \cdot \boldsymbol{J}_{n} = -q \left( R - G + \frac{\partial n}{\partial t} \right) \tag{3}$$

transport equations

$$\boldsymbol{J}_{\mathrm{p}} = -q \, p \, \mu_{\mathrm{p}} \nabla (\varphi - \lambda_{\mathrm{p}} \Theta_{\mathrm{p}}) - D_{\mathrm{p}} q \nabla (p) - k_{\mathrm{B}} p \, \mu_{\mathrm{p}} \nabla (T_{\mathrm{p}}) \tag{4}$$

$$\boldsymbol{J}_{\mathrm{n}} = -q\,n\,\mu_{\mathrm{n}}\nabla(\boldsymbol{\varphi} - \boldsymbol{\lambda}_{\mathrm{n}}\boldsymbol{\Theta}_{\mathrm{n}}) - D_{\mathrm{n}}q\nabla(\boldsymbol{n}) + k_{\mathrm{B}}n\,\mu_{\mathrm{n}}\nabla(T_{\mathrm{n}}) \tag{5}$$

energy balance equations

$$\nabla \cdot \mathbf{S}_{p} = \mathbf{J}_{p} \cdot \mathbf{E} - \frac{3}{2} k_{B} p \frac{T_{p} - T_{L}}{\tau_{wp}} - \frac{3}{2} k_{B} \frac{\partial}{\partial t} (pT_{p})$$

$$- \frac{3}{2} k_{B} T_{p} (R - G) - \frac{1}{2} q \lambda_{p} \left( \frac{p}{\tau_{wp}} - (G - R) \right) - \frac{1}{2} q \frac{\partial}{\partial t} (p\lambda_{p})$$

(6)

$$\begin{split} \nabla \cdot \boldsymbol{S}_{\mathrm{n}} &= \boldsymbol{J}_{\mathrm{n}} \cdot \boldsymbol{E} - \frac{3}{2} k_{\mathrm{B}} n \, \frac{T_{\mathrm{n}} - T_{\mathrm{L}}}{\tau_{\mathrm{wn}}} - \frac{3}{2} k_{\mathrm{B}} \frac{\partial}{\partial t} (n T_{\mathrm{n}}) \\ &- \frac{3}{2} k_{\mathrm{B}} T_{\mathrm{n}} (R - G) + \frac{1}{2} q \, \lambda_{\mathrm{n}} \left( \frac{n}{\tau_{\mathrm{wn}}} - (G - R) \right) + \frac{1}{2} q \, \frac{\partial}{\partial t} (n \lambda_{\mathrm{n}}) \end{split} \tag{7}$$

energy flux density equations

$$\boldsymbol{S}_{\mathrm{p}} = -\kappa_{\mathrm{p}} \nabla (T_{\mathrm{p}}) + \frac{5}{2} \frac{k_{\mathrm{B}}}{q} T_{\mathrm{p}} \boldsymbol{J}_{\mathrm{p}} + \frac{3}{2} \lambda_{\mathrm{p}} \boldsymbol{J}_{\mathrm{p}}$$

(8)

$$\boldsymbol{S}_{\mathrm{n}} = -\kappa_{\mathrm{n}} \nabla (T_{\mathrm{n}}) - \frac{5}{2} \frac{k_{\mathrm{B}}}{q} T_{\mathrm{n}} \boldsymbol{J}_{\mathrm{n}} + \frac{3}{2} \lambda_{\mathrm{n}} \boldsymbol{J}_{\mathrm{n}}$$

(9)

and equations for the quantum correction potential

$$\lambda_{\rm p} = -\frac{\gamma_{\rm p} \hbar^2}{6 \, m_{\rm p} q} \frac{\nabla^2 \sqrt{p}}{\sqrt{p}} \tag{10}$$

$$\lambda_{\rm n} = \frac{\gamma_{\rm n} \hbar^2}{6 \, m_{\rm n} \, q} \frac{\nabla^2 \sqrt{n}}{\sqrt{n}} \tag{11}$$

Further approaches are necessary for carrier mobilities, generation and recombination rates, diffusion coefficients and energy relaxation times, which are almost material dependent. Equations (1) to (11) are solved self-consistently for the variables ( $\varphi, p, n, T_p, T_n, \lambda_p, \lambda_n$ ). If equations (10) and (11) are neglected, i. e., for  $\lambda_p = \lambda_n = 0$ , the QHD model can be reduced to the conventional hydrodynamic (HD) model. If the carrier temperatures are set to lattice temperature and equations (6) to (9) are neglected, the quantum drift diffusion (QDD) model and additionally for  $\lambda_p = \lambda_n = 0$  the conventional drift diffusion (DD) model can be obtained. Solutions of the equations are achieved by a successive algorithm (the so

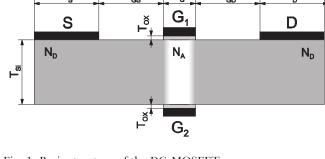

Fig. 1: Basic structure of the DG-MOSFET

called Gummel algorithm). For solving the partial differential equations a box method is used. The resulting non-linear equation systems are solved by the NEWTON-method and the corresponding linear equation systems by preconditioned gradient methods. All models are implemented fully three-dimensionally in the SIMBA program system [5], [6].

# 3 Basic structure simulation and verification

The starting point for the simulations is a basic structure represented in Fig. 1, as a functionally relevant detail of the real device. The different parameters are assumed as follows:

- gate length  $L_G = 30$  nm,

- source/drain lengths  $L_{\rm S}$  =  $L_{\rm D}$  = 100 nm,

- gate-to-source and gate-to-drain distances  $L_{\rm GS} = L_{\rm GD} = 100$  nm,

- silicon film thickness  $T_{\rm Si}$  = 20 nm,

- gate oxide thickness  $T_{ox} = 2 \text{ nm}$ ,

- channel doping  $N_{\rm A} = 1 \times 10^{16} \, \text{cm}^{-3}$

- source/drain doping  $N_D = 3 \times 10^{20} \text{ cm}^{-3}$ .

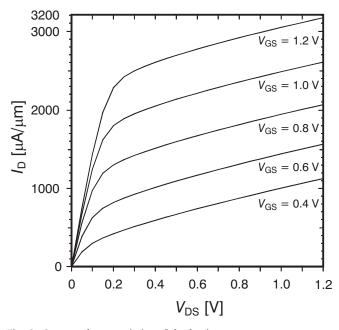

The simulated output characteristics drain current  $I_{\rm D}$  versus drain-to-source voltage  $V_{\rm DS}$  are plotted in Fig. 2 for

Fig. 2: Output characteristics of the basic structure

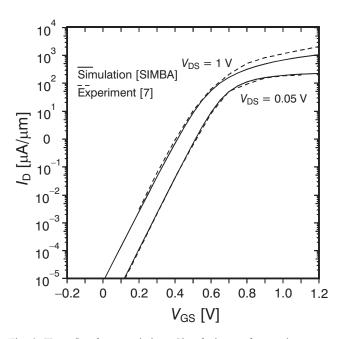

Fig. 3: Transfer characteristics - Simulation and experiment

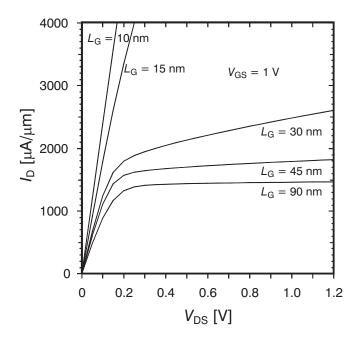

Fig. 4: Output characteristics at different gate lengths

different gate-to-source voltages  $V_{\rm GS}$ . Verification of the simulation results and calibration of the model parameters were done by comparison with experimental values from [7]. A structure similar to Fig. 1 with  $L_{\rm G}$ =45 nm,  $T_{\rm ox}$ =2.5 nm,  $N_{\rm D}$ =2×10<sup>20</sup> cm<sup>-3</sup> was simulated and compared with the measured values. The results represented in Fig. 3 show good agreement. A further successful verification was done by results from [8].

# 4 Parameter variation and optimization

To study the influence of the structure parameters on the electrical device characteristics, various parameters are modi-

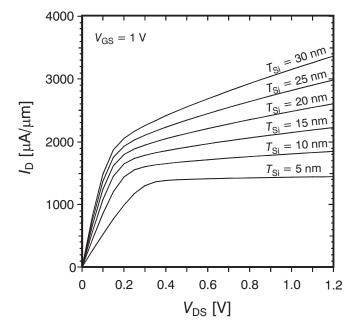

Fig. 6: Output characteristics at different channel thickness

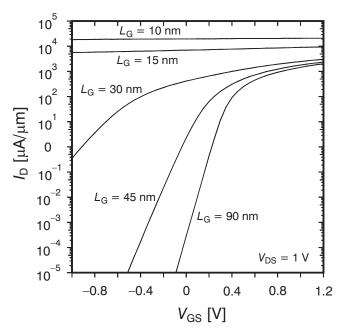

Fig. 5: Transfer characteristics at different gate lengths

fied. Figs. 4 and 5 depict the output and the transfer characteristics at different gate lengths. At shorter gate lengths a threshold voltage roll off can be observed as a typical short channel effect in the particular pinch-off behavior disappears for  $L_{\rm G}$  < 30 nm. At the same time, the drain saturation current increases strongly.

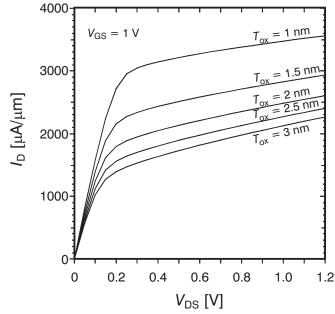

Variation results of the silicon film thickness are represented in Fig. 6. Thicker channels lead to larger drain currents, and also to a displacement of the threshold voltage toward smaller values. Therefore the film thickness should be not greater than 20 nm. Thinner gate oxides result in increasing drain currents (Fig. 7) and transconductances, and in a better pinch-off behavior. Therefore the smallest possible oxide thickness should be applied.

Fig. 7: Output characteristics at different gate oxide thickness

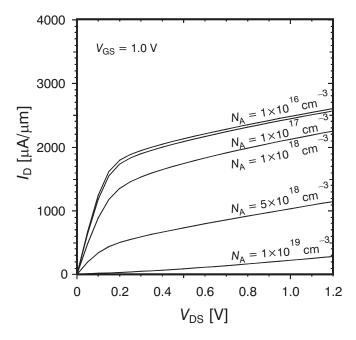

Fig. 8: Output characteristics at different channel doping

Fig. 9: Output characteristics at different source/drain doping

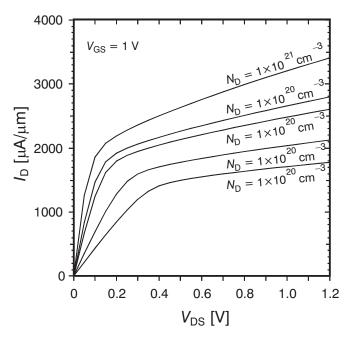

Variation of the channel doping causes a decrease in the drain current for doping densities greater than 10<sup>17</sup> cm<sup>-3</sup> (Fig. 8). The threshold voltage is strongly influenced by doping changes. For optimization of the structures, channel doping can be used to adjust the required threshold voltage. The source/drain doping should be high enough to reduce the series resistances, whereas the dopant diffusion into the channel has to be minimized to prevent short channel effects. In this case rapid thermal annealing processes are an essential equirement. Fig. 9 shows the corresponding output characteristics.

The knowledge gained from the different variations was used for the design of an optimized structure. A minimal

Fig. 10: Output characteristics of the optimized structure

Fig. 11: Transfer characteristics of the basic and the optimized structure

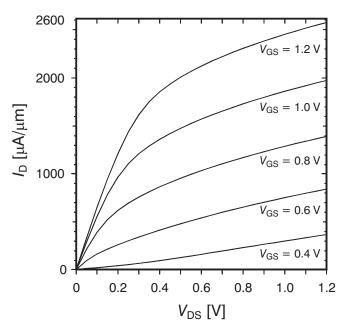

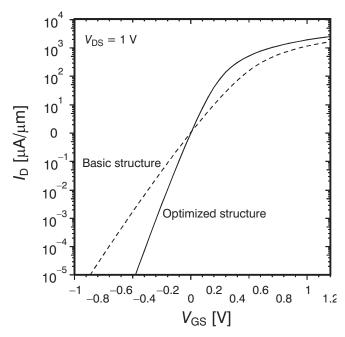

technologically practicable gate length of  $L_{\rm G}$ =15 nm and a gate oxide thickness of  $T_{\rm ox}$ =1.5 nm are specified. Further objectives are threshold voltage of  $V_{\rm Th}$ =0.1 V, large drain saturation current and improved dynamical behavior. After several iterations the further parameters are determined as follows:  $T_{\rm Si}$ =3 nm,  $N_{\rm A}$ =2.8×10<sup>19</sup> cm<sup>-3</sup>,  $N_{\rm D}$ =7×10<sup>20</sup> cm<sup>-3</sup>. The resulting output characteristics are represented in Fig. 10. Fig. 11 compares the transfer characteristic of the optimized and basic structure. An enlarged drain current as well as an improved transconductance can be observed.

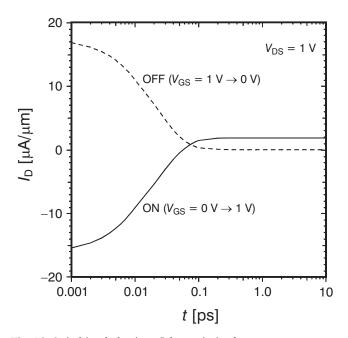

To determine the dynamical behavior, the gate-to-source voltage was switched from 0 V to 1 V to find the turn-on time  $(t_{\text{ON}})$  and from 1 V to 0 V to find the turn-off time  $(t_{\text{OFF}})$ .

Fig. 12: Switching behavior of the optimized structure

Fig. 12 shows the time response of the drain current. This provides the switching time of  $t_{\rm ON} = t_{\rm OFF} = 0.15$  ps. Compared with the basic structure the switching times are reduced by a factor of 0.6, primarily due to the structure reduction.

### **5 Conclusion**

The scaling down of planar bulk MOSFETs according the International Technology Roadmap for Semiconductors requires new structures such as multiple-gate MOSFETs A promising way to this is with the use of double-gate transistors. The implementation will be challenging, with numerous new and difficult issues. In this case numerical device simulation is essential. Variations of different structure parameters have been carried out to calculate the influence on device characteristics. Based on these results an optimized structure with a gate length of 15 nm was created. The optimized structure shows suppressed short channel effects and switching times of about 0.15 ps.

#### References

- [1] Gardner, C. L.: The Quantum Hydrodynamic Model for Semiconductor Devices. *SIAM J. Appl. Math.*, Vol. **54** (1994), No. 2, p. 409–427.

- [2] Chen, Z.: A Finite Element Method for the Quantum Hydrodynamic Model for Semiconductor Devices. *Comput. Math. Appl.*, Vol. **31**(1996), p. 17–26.

- [3] Wettstein, A., Schenk, A., Fichtner, W.: Quantum Device Simulation with the Density-Gradient Model on Unstructured Grids. *IEEE Trans. Electron Devices*, Vol. **48** (2001), No. 2, p. 279–284.

- [4] Selberherr, S.: Analysis and Simulation of Semiconductor Devices. Berlin, Germany, Springer-Verlag 1984.

- [5] Klix, W., Stenzel, R.: SIMBA-User Manual http://www.htw-dresden.de/~klix/simba/welcome.html.

- [6] Höntschel, J., Stenzel, R., Klix, W.: Simulation of Quantum Transport in Monolithic ICs Based on In0.53Ga0.47As-In0.52Al0.48As RTDs and HEMTs with a Quantum Hydrodynamic Transport Model. *IEEE Trans. on Electron Devices*, Vol. 51 (2004), No. 5, p. 684-692.

- [7] Lee, J. H., et al.: Super Self-Aligned Double-Gate (SSDG) MOSFETs Utilizing Oxidation Rate Difference and Selective Epitaxy. *IEDM*, *Tech. Digest*, (1999), p. 3.5.1–3.5.4

- [8] Vinet, M., et al.: Bonded Planar Double-Metal-Gate NMOS Transistor Down to 10 nm. *IEEE Electron Device Letters*, Vol. 26 (2005), p. 317–319

Prof. Dr. -Ing. habil Roland Stenzel e-mail: stenzel@et.htw-dresden.de

Leif Müller

Tom Herrmann

Prof. Dr. -Ing. habil Wilfried Klix

Department of Electrical Engineering

University of Applied Sciences Dresden Friedrich-List-Platz 1 D-01069 Dresden, Germany

http://ctn.cvut.cz/ap/