# Two-functional µBIST for Testing and Self-Diagnosis of Analog Circuits in Electronic Embedded Systems

### Dariusz Załęski, Romuald Zielonko

Gdansk University of Technology, Faculty of Electronics, Telecommunications and Informatics, Department of Metrology and Optoelectronics, ul. Gabriela Narutowicza 11/12, 80-233 Gdansk ,Poland

#### **ABSTRACT**

The paper concerns the testing of analog circuits and blocks in mixed-signal Electronic Embedded Systems (EESs), using the Built-in Self-Test (BIST) technique. An integrated, two-functional, embedded microtester ( $\mu$ BIST) based on reuse of signal blocks already present in an EES, such as microprocessors, memories, ADCs, DACs, is presented. The novelty of the  $\mu$ BIST solution is its extended functionality. It can perform 2 testing functions: functional testing and fault diagnosis on the level of localization of a faulty element. For functional testing the Complementary Signals (CSs), and for fault diagnosis the Simulation Before Test (SBT) vocabulary techniques have been used. In the fault vocabulary the graphical signatures in the form of identification curves in multidimensional spaces have been applied.

Section: RESEARCH PAPER

Keywords: Electronic embedded systems: built-in self-testers (BIST): functional testing: analog fault diagnostics

Citation: Dariusz Załęski, Romuald Zielonko, Two-functional µBIST for Testing and Self-Diagnosis of Analog Circuits in Electronic Embedded Systems, Acta IMEKO, vol. 3, no. 4, article 4, December 2014, identifier: IMEKO-ACTA-03 (2014)-04-04

Editor: Paolo Carbone, University of Perugia

Received October 10<sup>th</sup>, 2013; In final form October 10<sup>th</sup>, 2013; Published December 2014

**Copyright:** © 2014 IMEKO. This is an open-access article distributed under the terms of the Creative Commons Attribution 3.0 License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited

Funding: (none reported)

Corresponding author: Romuald Zielonko, e-mail: zielonko@eti.pg.gda.pl

#### 1. INTRODUCTION

Electronic embedded systems (EESs) with an embedded intelligent unit in a structure (usually in the form of a microcontroller), are widely used in many branches of industry, technology and science. The dominant group of EESs are mixed-signal systems. A common fact of these systems is the presence of analog circuits, since there always must be an interface to the real world. Mixed-signal EESs bring new challenges to the test problem of the analog circuits and blocks, because there is lack of general test methods and strategies.

The main direction of development of testing analog circuits in EESs is the built-in self-test (BIST) technique. In last years many specific solutions of BISTs dedicated for concrete circuits have been reported: oscillation-based BIST (OBIST) [1], digital reuse [2], histogram based [3], [4] dedicated for fully-differential stages [5], [6],  $\Sigma\Delta$  BIST [7], [8] and ADC BIST for AD converters. The common

feature of these solutions is hardware excess, i.e. the necessity to build an overhead hardware into the EES's structure, which introduces additional costs.

One promising solution to reduce the hardware overhead and testing costs is reuse of signal blocks already present in the EES (such as processors and memories) for a BIST creation. The new generations of microcontrollers (e.g. AT91SAM, ADuC814) have hardware resources (ADCs, DACs, timers, counters, analog comparators) that allow to generate stimulating signals and to measure responses of a circuit under test (CUT), as well as the computing power to realize of testing procedures. Therefore, the hardware and software resources of modern microcontrollers are sufficient for creation of microBISTs ( $\mu$ BISTs). These resources are sufficient, but simultaneously they are rather modest, thus special signals and procedures adequate to microcontroller resources must be used.

Some solution of the  $\mu$ BIST for functional testing based on shape designed complementary signals (CSs) [9], [10],

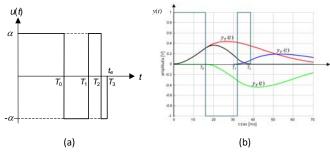

Figure 1. An example of the 3<sup>rd</sup> order  $T_r$ -parameter CS (a) and CUT responses  $y_{T_i}(t)$  to each impulse of  $T_r$ -parameter CS and its resultant response y(t) (b).

[11] has been proposed by the authors in [12]. The disadvantage of this solution is poor functionality, limited only to functional testing.

The novelty of the solution presented in this paper is the extended functionality of the  $\mu$ BIST, including both functional and diagnostic testing. In the proposed solution (named the integrated, two-functional  $\mu$ BIST) for functional testing, complementary signals and for fault diagnosis SBT (simulation before test) techniques have been used.

The paper is organized as follows: Section II presents the CS method for functional testing. Section III describes a vocabulary SBT technique for diagnostic testing. Section IV presents an experimental realization of the integrated two-functional  $\mu$ BIST and its verification in an exemplary EES.

### 2. DESCRIPTION AND INVESTIGATION OF THE CS METHOD FOR FUNCTIONAL TESTING

The essence of this method is stimulation of the CUT by a special shape-designed CS signal, whose parameters are matched to poles of the CUT's transfer function. Two

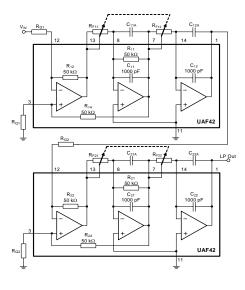

Components values of the 1st section:  $R_{G1}\text{=}52.22~k\Omega$   $R_{Q1}\text{=}83.56~k\Omega$   $R_{F11},R_{F12}\text{=}15.28~k\Omega$   $C_{11A}\text{=}1052~nF$   $C_{12A}\text{=}1054~nF$

Components values of the 2<sup>nd</sup> section:  $R_{G2}{=}51.84~k\Omega$   $R_{O2}{=}17.43~k\Omega$   $R_{F21}{,}R_{F22}{=}14.95~k\Omega$   $C_{11A}{=}1040~nF$

C<sub>12A</sub>=1041 nF

Functional parameters:

$f_c$ =10 Hz  $\omega_c$ =62.8319 rad/s  $Q_1$ =0.54119  $Q_2$ =1.30655  $s_1$ ,  $s_2$ =-58.0491  $\pm$  4.0447i  $s_3$ ,  $s_4$ =-24.0447  $\pm$  8.0491i

Figure 2. Schematic diagram of investigated  $4^{\rm th}$  order Butterworth low-pass filter and its component values.

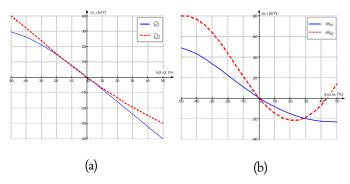

Figure 3. Responses  $y(t_e)=f(\Delta Q_i/Q_i)$  and  $y(t_e)=f(\Delta \omega_{nil}/\omega_{ni})$  of the tested 4<sup>th</sup> order LPF as a function of  $Q_1$  and  $Q_2$  factors deviation (a) and  $\omega_{n1}$  and  $\omega_{n2}$  angular frequencies deviation (b).

kinds of CS signals has been investigated in [14]: i-parameters CS (with variable impulse amplitude i) and *Ti*-parameters CS (with variable impulse width *Ti*).

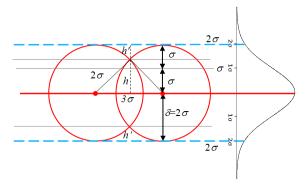

A typical example of  $T_t$ -parameters CS signal is shown in Figure 1a. The testing principle is explained in Figure 1b. The first impulse of the CS signal drives the CUT into an initial state  $y_{70}(t)$ , whereas the remaining impulses  $y_{71}(t)$ ,  $y_{72}(t)$  compensate it, in the manner shown in the figure, that the CUT response  $y(t_e)$  reaches a zero state at the signal end time  $t_e$ . Such situation takes place when the CUT is in its nominal state. In a faulty state, when transfer function poles are deviating from nominal values, the CUT response after the end of stimulation is not compensated  $(y(t_e) \neq 0)$ . The sample value of the CUT response  $y(t_e)$  depends on deviation of transfer function parameters from the nominal state. So, it can be used for functional testing of the CUT transfer function.

The CS method has been widely investigated, at first via simulations and then via physical experiments, on the example of testing of a 4<sup>th</sup> order Butterworth low-pass filter (LPF). The structure of the filter, as well as nominal functional parameters and component values are shown in Figure 2. The filter was composed with two BiQuad sections realized on the integrated circuit UAF42. The transfer function of the 4<sup>th</sup> order Butterworth LPF is described by the following formula:

$$G_{IV}(s) = \frac{\omega_{n1}^2 \omega_{n2}^2}{\left(s^2 + \frac{\omega_{n1}}{Q_1} s + \omega_{n1}^2\right) \times \left(s^2 + \frac{\omega_{n2}}{Q_2} s + \omega_{n2}^2\right)}$$

(1)

where:  $\omega_{n1}$ ,  $\omega_{n2}$  are filter cut-off angular frequencies,  $Q_1$ ,  $Q_2$  are quality factors of the 1<sup>st</sup> and 2<sup>nd</sup> section.

The filter was stimulated by a matched  $T_{i}$ -parameter CS signal with 1 V impulses and with following  $T_{i}$ -parameters:  $T_{0} = 15.916$  ms,  $T_{1} = 37.393$  ms,  $T_{2} = 57.185$  ms,  $T_{3} = 70.397$  ms,  $T_{4} = t_{e} = 75.027$  ms.

The investigation results of the deviation influence of both: quality factors  $Q_1$ ,  $Q_2$  and angular frequencies  $\omega_{n1}$ ,  $\omega_{n2}$  on the CUT's output signal, are presented in Figure 3.

It is seen from plots shown in the figure, relations  $y(t_e) = f(\Delta Q_i/Q_i)$  and  $y(t_e) = f(\Delta \omega_{ni}/\omega_{ni})$  are convenient to implement. The  $y(t_e) = f(\Delta Q_i/Q_i)$  relations are linear in a wide range of  $\Delta Q_i/Q_i$  deviation (±50%). The testing

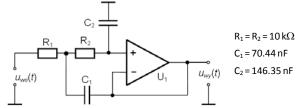

Figure 4. The 2nd order low-pass filter.

sensitivity is about 0.8 mV/1%. The  $y(t_e) = f(\Delta \omega_{ni}/\omega_{ni})$  relations are slightly nonlinear and the testing range for positive deviations of  $(\Delta \omega_{ni}/\omega_{ni})$  is limited to 25%. Testing sensitivities are not equal for different BiQuad sections of the filter. For the 1<sup>st</sup> section the sensitivity is about 0.5 mV/1% and for the 2<sup>nd</sup> section it is about 1 mV/1%.

In all investigated cases testing sensitivities are high enough for CUT functional testing. The CUT's output response signals  $y(t_e)$  are easy to measure using the AD converter available in the

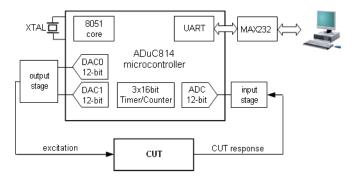

microcontroller ADuC814, chosen for the realization of the two-functional  $\mu$ BIST. Hardware resources of this microcontroller (12-bit ADC and DACs and 3x16-bit programmable counters) are good enough for the generation of CS signals with adequate precision and for accurate measurement of CUT's output responses.

In [14] the metrological properties of the i-parameters and Ti-parameters CSs have been widely investigated and compared. The following conclusions should be emphasized:

- both signals have similar sensitivities to deviations of CUT functional parameters,

- more predestined for application in the  $\mu$ BIST are  $T_r$ -parameters CSs. They are shorter, easier to generate using microcontroller resources and can be optimized to the CUT structure by matching the width of the 1<sup>st</sup> impulse. The most useful is a unipolar  $T_r$ -parameter CS.

Generally, we can conclude that unipolar *Ti*-parameters CSs signals are suitable for application in a  $\mu$ BIST for functional testing of analog circuits and blocks in EESs, which appears as the first function of an integrated  $\mu$ BIST. The CS method might be useful in the low frequency range, up to about 10 kHz.

### 3. DESCRIPTION AND INVESTIGATION OF THE SBT DIAGNOSTIC METHOD

Figure 6. The identification curves for range  $0.5p_{i\,nom} \le p_i \le 1.5p_{i\,nom}$ .

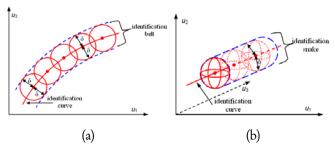

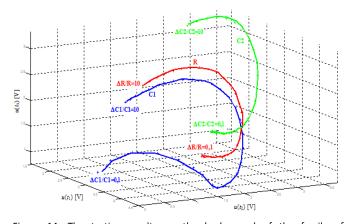

For diagnostic testing of analog circuits in the EESs, which appears as the second function of an integrated  $\mu$ BIST, the vocabulary SBT method has been chosen, with graphical fault signatures in the form of identification curves in multidimensional measurement spaces.

Such a form of the fault vocabulary has two advantages:

- identification curves can be scaled, thus they make fault localization and also identification possible,

- it is possible to introduce an additional distinctive feature of the measurement signal to increase the dimension of the measurement space, and in consequence rarefying curves in the space. In result it enables to increase distinctivity of fault localization and to decrease the fault masking effect of parameter tolerances.

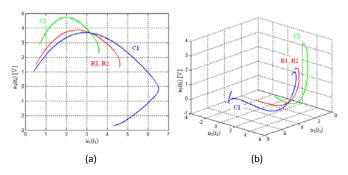

We investigated this method using a 2D and 3D measurement space based on the samples  $u_1(t_1)$ ,  $u_2(t_2)$ ,...,  $u_k(t_k)$  of a CUT output response at properly chosen time moments, taking into account 2 cases: toleranceless CUTs and CUTs with real tolerances of elements.

At first, for simplification we explain this method on the example of fault diagnosis of the 2<sup>nd</sup> order Butterworth LPF (Figure 4), without taking into account tolerances.

For the filter, on the basis of 2 or 3 samples of its output response to a single square-impulse stimulation, we can

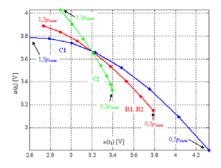

Figure 7. The circuit diagram the 3<sup>rd</sup> order Butterworth LPF (a) and families of dispersed identification curves (belts) in the 3D space (b).

Figure 8. Models of identification belts and snakes in 2D (a) and 3D (b) spaces.

obtain the fault vocabulary in the form of a family of identification curves on a plane (for 2 samples  $u_1(t_1)$ ,  $u_2(t_2)$ ) or in 3D space (for 3 samples  $u_1(t_1)$ ,  $u_2(t_2)$ ,  $u_3(t_3)$ ) as shown in Figure 5, for wide a range of parameters change:  $0.1p_{inom} \le p_i \le 10p_{inom}$ .

In practice, the soft faults are diagnosed in narrower ranges:  $\pm 50\%$  (0.5 $p_{inom} \le p_i \le 1.5p_{inom}$ ) or even  $\pm 25\%$ . The family of scaled identification curves in the range  $\pm 50\%$  is shown in Figure 6. In this range, as it is seen, the curves are smooth and easy to point interpolation. For such fault signature classification a simple conventional point distance classifier can be used. The required memory size for a fault vocabulary is moderate. For example, in case of a fault vocabulary in 3D space with 10 identification curves and 50 interpolation points for each, the memory size is about 3750 bytes.

The toleranceless version of the SBT method can be useful for fault diagnosis of circuits with small parameter tolerances  $<\pm0.5\%$ . It seems to be of little use in practice.

In practice, analog circuits have higher tolerances (in real circuits 2%-5%), which cause dispersion of identification curves in the measurement space. The dispersed curves form in the 2D space a kind of identification belts, and in the 3D space they form the identification snakes as shown in Figure 7. Such families can be obtained from simulations using the Monte Carlo method. Identification belts and snakes in the general case have variable cross sections, but for moderate CUT's tolerances (±2%) they can be assumed constant.

The identification belts and snakes can be used for soft fault diagnosis, but their more sophisticated description as graphic signatures in the fault vocabulary is needed. An

Figure 9. A piece of identification belt model for estimation of confidence coefficient  $\alpha$ .

Figure 10. The block diagram of the realized  $\mu BIST.$

appropriate classifier fitted to these signatures must be used.

For modeling of the identification belts and snakes and description in a vocabulary, we have used models shown in Figure 8, for 2D and 3D spaces. The belts are modeled by the set of circles with radius of  $\delta$  around the interpolation points  $P_i$  of the nominal identification curve. The sets of spheres around the interpolation points, with radius of  $\delta$ , model the identification snakes. They are described by two factors: co-ordinates of interpolating points of the nominal identification curve, and the scaling factor  $\delta$ , which characterizes the dispersion of the curve in these points.

Different versions of the method were investigated, but for implementation in the  $\mu$ BIST based on the ADuC814 microcontroller, we have used the 3D version of the method with the following assumptions: all identification snakes have a constant scaling factor  $\delta = 2\sigma$ , where  $\sigma$  is the standard deviation and the distance between interpolation points  $P_i$  is  $1.5\delta = 3\sigma$ .

The confidence coefficient  $\alpha$  depends on the distance between adjacent interpolation points  $P_i$ . For a distance equal to  $3\sigma$ , based on the drawing in Figure 9 that shows a piece of the identification belt model in 2D space, the value of the confidence coefficient  $\alpha$  has been estimated as  $\alpha = 0.954-0.035\approx 0.92$  [14]. This value is sufficient for using this model in practice.

The testing procedure is simple and based on sequential checking of the distance between the measurement point  $P_m$  and the interpolating points  $P_i$  of identification curves with the use of a conventional point distance classifier.

Description of the identification snakes in the 3D fault vocabulary (using co-ordinates of interpolation points  $P_i$  and scaling factor  $\delta$ ) for the CUT with 10 elements requires 3000 bytes, for a fault range of  $\pm 50\%$  In a testing procedure, 9 operations must be performed for the checking of each interpolating point  $P_i$  of the identification curve in the fault vocabulary. Thus, about 5000 operations are required for testing a 10 element CUT. It can easily be realized in an acceptable time of < 0.1 seconds.

Based on simulation investigations, we can conclude that the real tolerance version of the SBT method can be easily realized in the ADuC814 microcontroller, but it needs experimental verification in a physically realized  $\mu$ BIST.

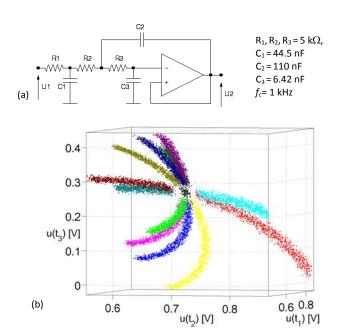

Figure 11. The circuit diagram and the picture of the realized  $\ensuremath{\mu \text{BIST}}.$

## 4. EXPERIMENTAL REALIZATION AND VERIFICATION OF AN INTEGRATED TWO-FUNCTION $\mu BIST$

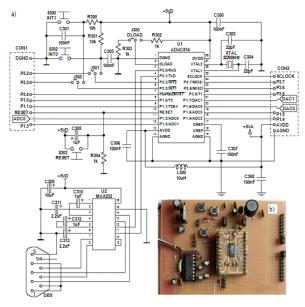

On the basis of hardware and software resources of the Analog Devices microcontroller ADuC814, an integrated  $\mu$ BIST for functional and fault diagnostic testing of analog circuits in the EESs has been physically realized and investigated in an experimental embedded system. The

Figure 12. The simulated and measured CUT responses  $y(t_e)=f(\Delta Q_i/Q_i)$  as function of  $Q_1$  (a) and  $Q_2$  (b) deviations.

Figure 13. The simulated and measured CUT responses  $y(t_e)=f(\Delta\omega_{ni}/\omega_{ni})$  as a function of  $\omega_{n1}$  (a) and  $\omega_{n2}$  (b) deviations.

structure of the  $\mu$ BIST is shown in Figure 10 and its circuit diagram is shown in Figure 11. Almost all additional elements surrounding the ADuC814 chip are present in each EES and they are necessary for proper functioning of the microcontroller.

The microcontroller was programmed with software realizing two testing procedures of functional testing (using unipolar *Ti*-parameter CS signals) and the diagnostic testing using the SBT method, in a 3D version.

The  $\mu$ BIST was investigated experimentally, on the basis of physical testing of some real analog circuits, mainly filters. Different variants of the CS method for functional testing and the SBT method for fault diagnosis have been experimentally investigated. Various deviations of  $Q_i$ ,  $\omega_n$

Figure 14. The testing results on the background of the family of identification curves for the  $2^{\rm nd}$  order LPF.

parameters and values of soft faults for each  $p_i$  element were physically entered to real CUTs. The experimental results were compared with simulation ones.

For the CS method of functional testing a comparison between experimental and simulation results is shown in Figure 12. In simulation and experimental investigations the same CS signal level of 1 V has been used. Figure 12 shows experimental (blue curve) and simulated (red curve) plots:  $y(t_e) = f(\Delta Q_1/Q_1)$  and  $y(t_e) = f(\Delta Q_2/Q_2)$  concerning dependences of the CUT response signal on  $Q_1$  and  $Q_2$  deviations. Analogous plots of  $y(t_e) = f(\Delta \omega_{n2}/\omega_{n1}/\omega_{n1})$  and  $y(t_e) = f(\Delta \omega_{n2}/\omega_{n2})$ , concerning deviations of  $\omega_{n1}$  and  $\omega_{n2}$ , are shown in Figure 13.

As it is seen in both figures, experimental results are very close to the simulated ones. Experimental and simulated plots have the same shapes and they are very close, especially in the range of ±10% deviations. Higher differences out of this range do not matter in practice, because

OUT.

CUT response – parameter deviations can be modeled on the basis of experimental data.

In simulations and experimental investigations of this method, CS signals with a level of 1 V have been used. For such signals the threshold level of functional testing is on the level of a few percent for  $\Delta Q_i/Q_i$  and  $\Delta \omega_{ni}/\omega_{ni}$  deviations. In practice CUT stimulation with higher level of CS, up to 5 V, can be used. It enables to obtain a lower threshold level for both parameter deviations  $\Delta Q_i/Q_i$  and  $\Delta \omega_{ni}/\omega_{ni}$ , below 1%.

The convergence of the simulation and experimental results confirms the previous conclusions from simulation investigations. The method can be used in a frequency range up to 10 kHz.

For the SBT method of fault diagnostics the 2<sup>nd</sup> order LPF shown in Figure 4 was experimentally investigated. Figure 14 shows the results of the investigations (in the form of crosses) in comparison with simulated identification curves.

As it is seen, in this case the experimental results and simulated curves are very close in a wide investigated range  $0.1p_{inom} \le p_i \le 10p_{inom}$ . This example and other investigations presented in [14] confirm the usefulness of this SBT diagnostic method for application in a  $\mu$ BIST. It can be utilized for fault localization in analog circuits with a moderate number of components of about 10, like: filters, equivalent circuits of signal transmission lines or non-electrical objects (e.g. sensors) modeled in the form of multi-element two-terminals or two-ports. The method makes localization of single soft faults and ambiguity groups possible as well as detection of multiple faults.

On the basis of both above methods of functional and diagnostic testing, the final version of the two-functional  $\mu$ BIST has been programmed in the microcontroller ADuC814. In both methods unipolar input signals with an extended impulse level of 5 V have been used. Some  $\mu$ BIST properties are given below:

- Threshold level for functional testing deviations  $\Delta Q_i/Q_i$  is 1% and for deviations  $\Delta \omega_{ni}/\omega_{ni}$  is about 0.8%.

- Mean functional testing time of the 4th order LPF is

- about 90 ms. Mean time of diagnostic testing of the same filter is about 600 ms.

- The required microcontroller memory size for functional testing is 476 bytes and for diagnostic testing it is 2469 bytes (total 2945 bytes).

There are many possibilities of improving the  $\mu$ BIST, mainly by using more advanced 16- or 32-bit microcontrollers and a neural network classifier of fault signatures. Recently, a neural classifier with two-central basis functions has been elaborated and reported in [16]. It is well suited to application in  $\mu$ BISTs. We are going to implement this classifier in the new version of the integrated  $\mu$ BIST.

#### 5. CONCLUSIONS

In this paper the new concept, methodology and solution of an integrated, two-functional µBIST, dedicated to testing of analog parts of electronic embedded systems, have been presented. The µBIST integrates two functions: functional testing and fault diagnosis on the level of localization soft faulty component. The µBIST has been constructed on the basis of reusing a microcontroller and other blocks already present in each EES. We showed that contemporary microcontrollers, like the ADuC814, have sufficient hardware and software resources to design µBISTs for functional and diagnostic testing of linear analog circuits in the low frequency range (0.1 Hz - 10 kHz) such as: filters, signal transmission paths or some non-electrical objects (e.g. sensors) modeled by electrical schemes. There are perspectives of further improvement of the presented μBIST, using 16- or 32-bit microcontrollers and a neural classifier.

### **REFERENCES**

- [1] Toczek W.: "An oscillation-based built-in test scheme with AGC loop". Measurement, vol. 41, no. 2 pp. 160-168, 2008.

- [2] Andrade A. Q.: "Test Planning for Mixed-Signal SoCs and Analog BIST: a Case Study". IEEE Transact. on Instrumentation and Measurement, vol.54, no. 4, 2005.

- [3] Toczek W., Kowalewski M., Zielonko R.: "Histogram-Based Feature Extraction Technique Applied for Fault Diagnosis of Electronic Circuits". Proceedings of the 10th Int. Conference on Technical Diagnosis, IMEKO TC-10, pp. 27-32, Budapest, 2005

- [4] Ren J., H. Ye: "A Novel Linear Histogram BIST for ADC". Ninth International Conference on Solid-State and Integrated-Circuit Technology, pp. 2099-2102, Beijing, 2008.

- [5] Stratigopoulos H. G. D.: "An Adaptive Checker for Fully Differential Analog Code". IEEE Journal of Solid-State Circuits, vol. 41, no. 6, pp. 1421-1429, 2006.

- [6] Toczek W.: "Self-testing of fully differential multistage circuits using common-mode excitation". Microelectronics Reliability, pp. 1890-1899, 2008.

- [7] Huang J. L., Cheng K. T.: "A Sigma-Delta Modulation Based BIST Scheme for Mixed-Signal Circuits". Proceedings of the 2000 Asia And South Pacific Design Automation Conference, pp. 605-610, Japan, 2000.

- [8] Toczek W.: "Analog fault signature based on sigma-delta modulation and oscillation test methodology". Metrology And Measurement Systems, vol. XI, no. 4, pp. 363-375, 2004.

- [9] Schreiber H. H.: "Fault dictionary based upon stimulus design", IEEE Transactions on Circuits and Systems, vol. 26, no. 7, pp. 529-537, 1979.

- [10] Bartosiński B., Zielonko R.: "New classes of complementary signals". Electronic Letters, vol.23, no. 9, pp. 433-434, Apr. 1987

- [11] Bartosiński B., Zielonko R.: "Application of Complementary Measuring Signals to Testing of Analog Circuits", Third International Symposium on Methods and Models in Automation and Robotics, Poland, pp. 527-532, 1996.

- [12] Załęski D., Bartosiński B., Zielonko R.: "Application of Complementary Signals in Built-In Self Testers for Mixed-Signal Embedded Electronic Systems". IEEE Transactions on Instrumentation and Measurement, vol. 59, 2010, pp. 345-352.

- [13] Czaja Z., Zielonko R.: "Fault diagnosis in electronic circuits based on bilinear transformation in 3-D and 4-D spaces". IEEE Transactions On Instrumentation and Measurement, vol. 52, no. 1, pp. 97-102, 2003.

- [14] Załęski D., The Autodiagnostics of Electronic Embedded Systems, PhD dissertation, Gdansk University of Technology, 2013. (in Polish).

- [15] Czaja Z., Załęski D.: "Implementation of an input-output method of diagnosis of analog electronic circuits in embedded systems". Proceedings of the 10th IMEKO TC10 International Conference on Technical Diagnostics, pp. 145-150, Budapest, 9-10 June 2005.

- [16] Kowalewski M., The tolerance-proof vocabulary methods of fault diagnostic in electronic circuits using dedicated faults classifier with neural network, PhD dissertation, Gdansk University of Technology, 2012 (in Polish).